## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

"Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

"Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

## **User's Manual**

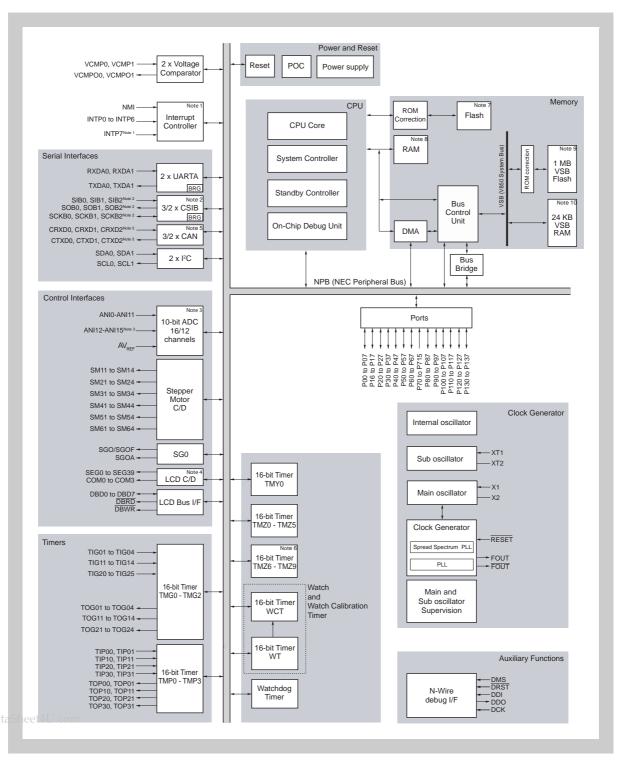

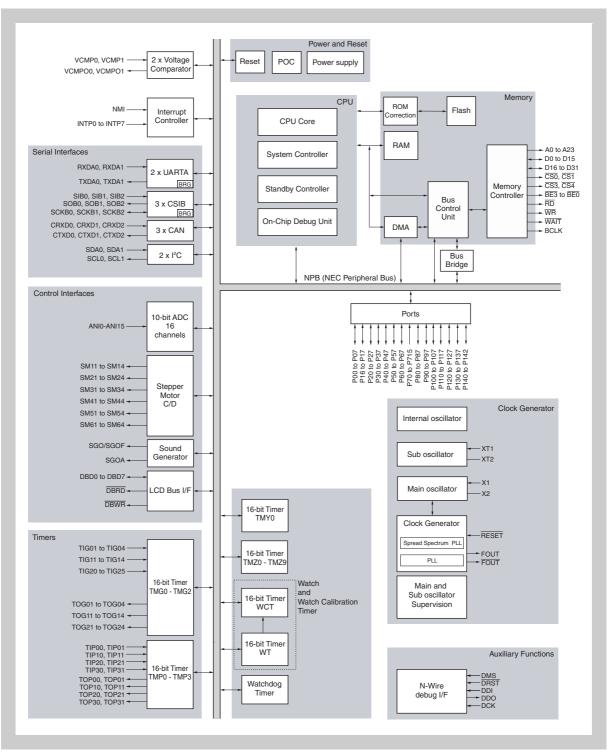

# V850E/Dx3 - DJ3/DL3

# 32-bit Single-Chip Microcontroller

## **Hardware**

V850E/DJ3: µPD70F3421 µPD70F3422 µPD70F3423 µPD70F3424 µPD70F3425 µPD70F3426A V850E/DL3: μPD70F3427

## **Notes for CMOS Devices**

## (1) Precaution against ESD for semiconductors

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

#### (2) Handling of unused input pins for CMOS

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

#### (3) Status before initialization of MOS devices

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

## **Legal Notes**

- The information in this document is current as of <publishing month year>.

The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or data books, etc., for the most up-to-date specifications of NEC Electronics products. Not all products and/or types are available in every country. Please check with an NEC sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any

means without prior written consent of NEC Electronics. NEC Electronics

assumes no responsibility for any errors that may appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC Electronics products listed in this document or any other liability arising from the use of such NEC Electronics products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this

document are provided for illustrative purposes in semiconductor product

operation and application examples. The incorporation of these circuits,

software and information in the design of customer's equipment shall be

done under the full responsibility of customer. NEC Electronics assumes no

responsibility for any losses incurred by customers or third parties arising

from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC Electronics products, customers must incorporate sufficient safety measures in their design, such as redundancy, firecontainment and anti-failure features.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific".

The "Specific" quality grade applies only to NEC Electronics products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

"Standard": Computers, office equipment, communications

equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and

industrial robots.

"Special": Transportation equipment (automobiles, trains, ships,

etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).

"Specific": Aircraft, aerospace equipment, submersible repeaters,

nuclear reactor control systems, life support systems and

medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact NEC Electronics sales representative in advance to determine NEC Electronics 's willingness to support a given application.

- Note 1. "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

- 2. "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).

## **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- · Device availability

- · Ordering information

- · Product release schedule

- · Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- · Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

#### **NEC Electronics Corporation**

1753, Shimonumabe, Nakahara-ku, Kawasaki, Kanagawa 211-8668, Japan Tel: 044 4355111 http://www.necel.com/

#### [America]

### NEC Electronics America, Inc.

2880 Scott Blvd. Santa Clara, CA 95050-2554,I U.S.A.

Tel: 408 5886000 http://www.am.necel.com/

#### [Europe]

#### **NEC Electronics (Europe) GmbH**

Arcadiastrasse 10 0472 Düsseldorf, Germany Tel: 0211 65030 http://www.eu.necel.com/

#### **United Kingdom Branch**

Cygnus House, Sunrise Parkway Linford Wood, Milton Keynes MK14 6NP, U.K. Tel: 01908 691133

### Succursale Française

9, rue Paul Dautier, B.P. 52 78142 Velizy-Villacoublay Cédex France

Tel: 01 30675800

#### Sucursal en España

Juan Esplandiu, 15 28007 Madrid, Spain Tel: 091 5042787

## Tyskland Filial

Täby Centrum Entrance S (7th floor) 18322 Täby, Sweden Tel: 08 6387200

#### Filiale Italiana

Via Fabio Filzi, 25/A 20124 Milano, Italy Tel: 02 667541

#### **Branch The Netherlands**

Steijgerweg 6 5616 HS Eindhoven, The Netherlands Tel: 040 2654010

#### [Asia & Oceania]

#### NEC Electronics (China) Co., Ltd

7th Floor, Quantum Plaza, No. 27 ZhiChunLu Haidian District, Beijing 100083, P.R.China Tel: 010 82351155 http://www.cn.necel.com/

### NEC Electronics Shanghai Ltd.

Room 2511-2512, Bank of China Tower, 200 Yincheng Road Central, Pudong New Area, Shanghai 200120, P.R. China Tel: 021 58885400 http://www.cn.necel.com/

#### **NEC Electronics Hong Kong Ltd.**

12/F., Cityplaza 4, 12 Taikoo Wan Road, Hong Kong Tel: 2886 9318 http://www.hk.necel.com/

#### **NEC Electronics Taiwan Ltd.**

7F, No. 363 Fu Shing North Road Taipei, Taiwan, R.O.C. Tel: 02 27192377

#### **NEC Electronics Singapore Pte. Ltd.**

238A Thomson Road, #12-08 Novena Square, Singapore 307684 Tel: 6253 8311 http://www.sg.necel.com/

### **NEC Electronics Korea Ltd.**

11F., Samik Lavied'or Bldg., 720-2, Yeoksam-Dong, Kangnam-Ku, Seoul, 135-080, Korea Tel: 02-558-3737 http://www.kr.necel.com/

### **Preface**

Readers This manual is intended for users who want to understand the functions of the

concerned microcontrollers.

**Purpose** This manual presents the hardware manual for the concerned microcontrollers.

Organization This system specification describes the following sections:

• Pin function

CPU function

• Internal peripheral function

**Module instances** These microcontrollers may contain several instances of a dedicated module.

In general the different instances of such modules are identified by the index

"n", where "n" counts from 0 to the number of instances minus one.

Legend Symbols and notation are used as follows:

• Weight in data notation: Left is high order column, right is low order

column

• Active low notation:  $\overline{xxx}$  (pin or signal name is over-scored) or

/xxx (slash before signal name)

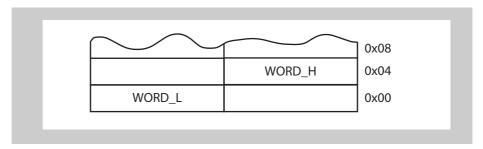

Memory map address: High order at high stage and low order at low

stage

Note Additional remark or tip

Caution Item deserving extra attention

Numeric notation: • Binary: xxxx or xxx<sub>B</sub>

• Decimal: xxxx

Hexadecimal: xxxx<sub>H</sub> or 0x xxxx

Prefixes representing powers of 2 (address space, memory capacity):

• K (kilo):  $2^{10} = 1024$

M (mega): 2<sup>20</sup> = 1024<sup>2</sup> = 1,048,576

G (giga): 2<sup>30</sup> = 1024<sup>3</sup> = 1,073,741,824

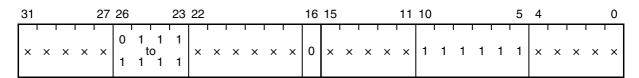

**Register contents:** X, x = don't care

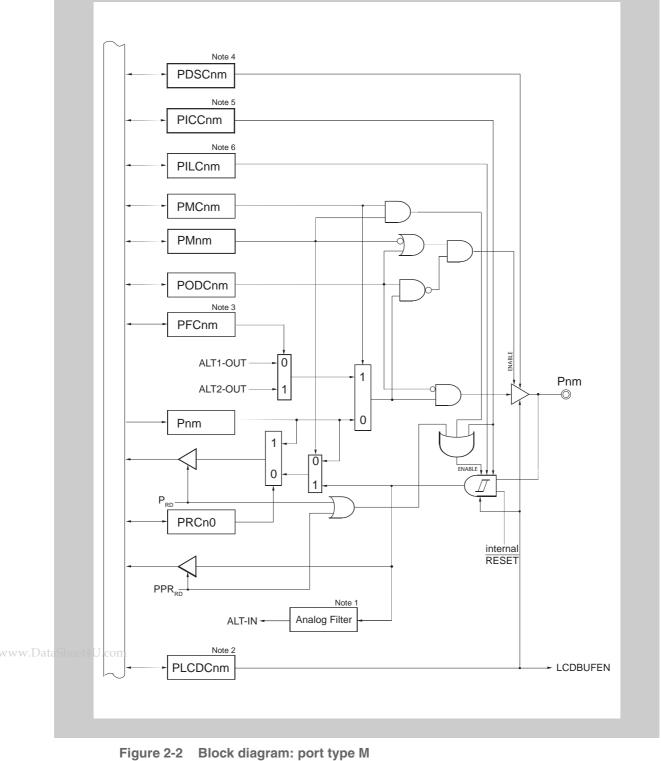

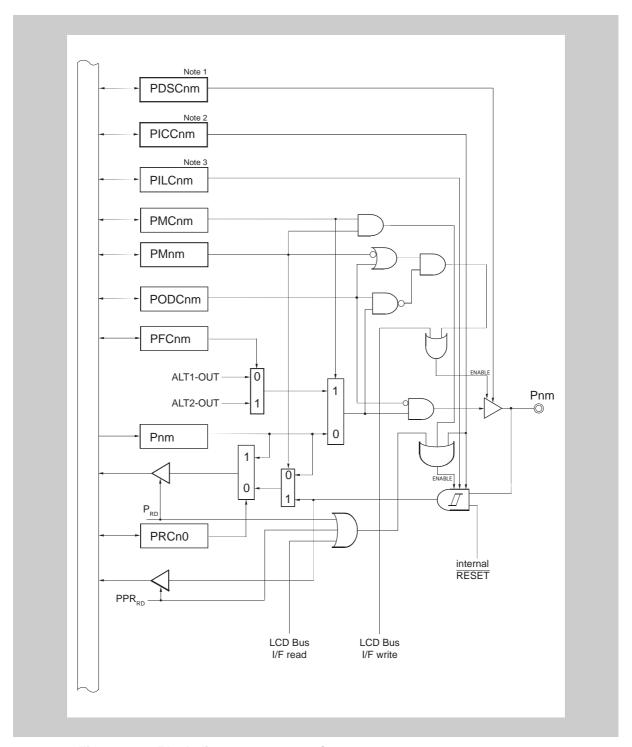

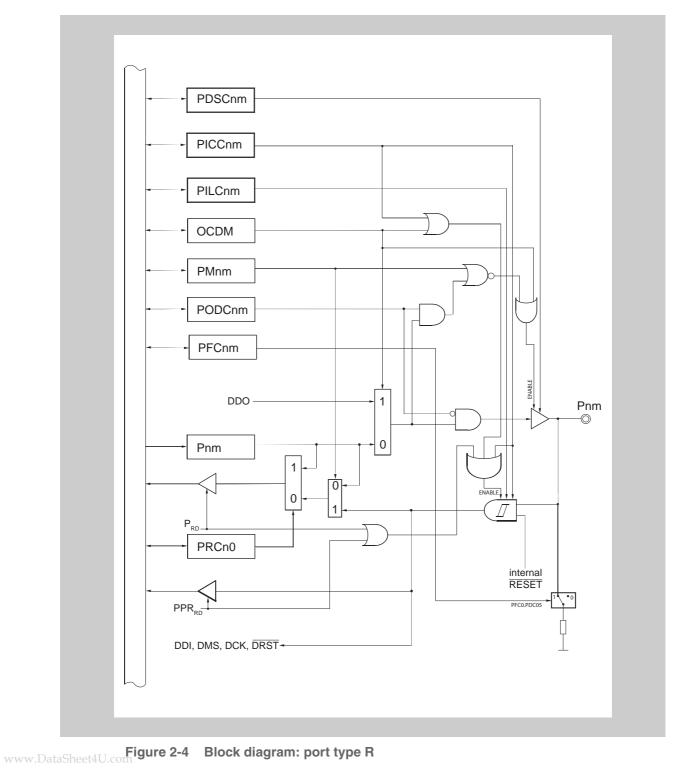

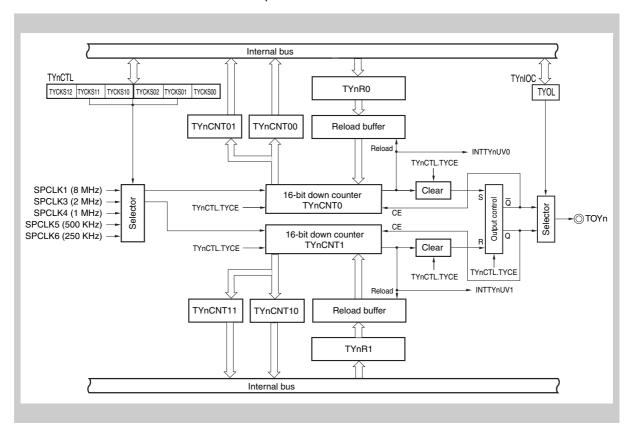

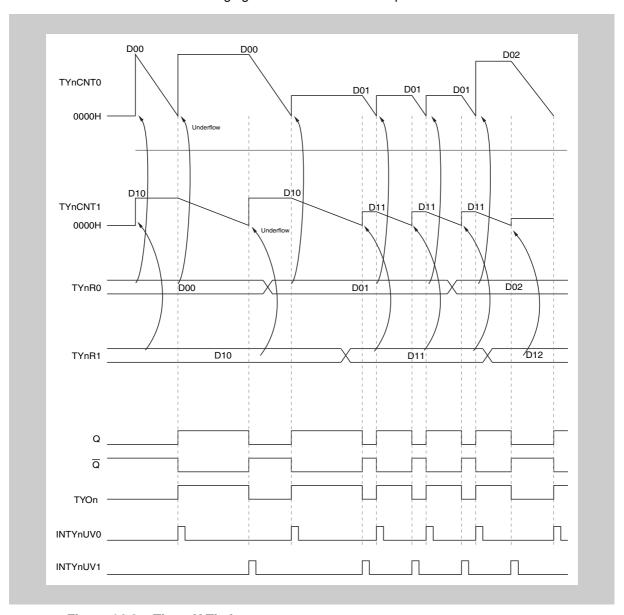

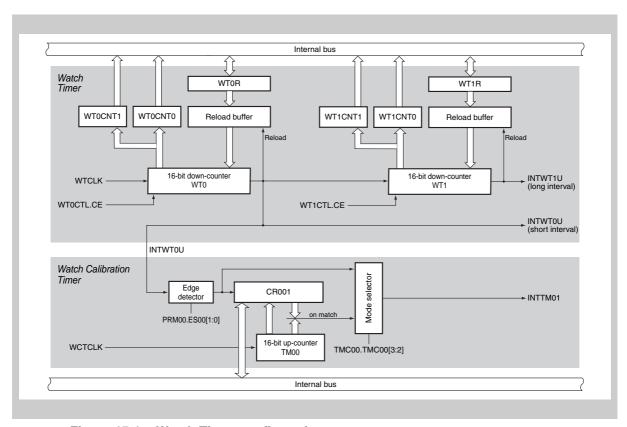

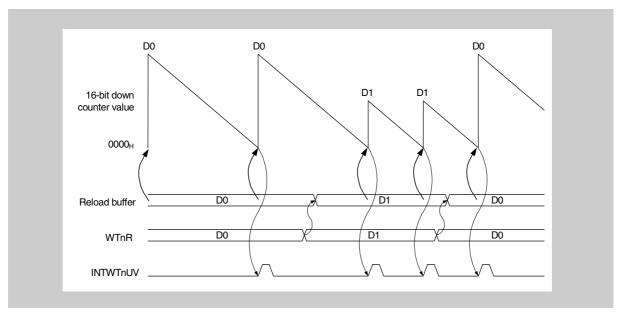

Diagrams Block diagrams do not necessarily show the exact wiring in hardware but the

functional structure.

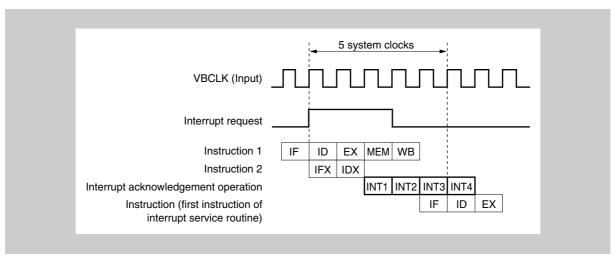

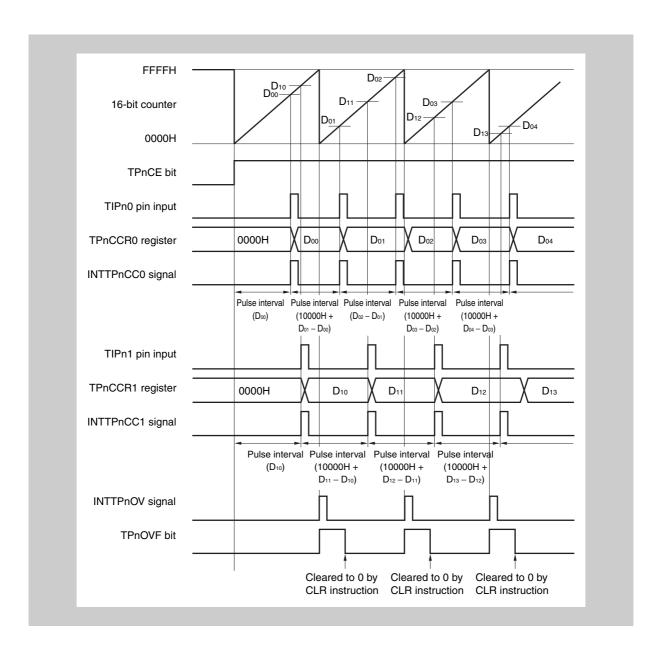

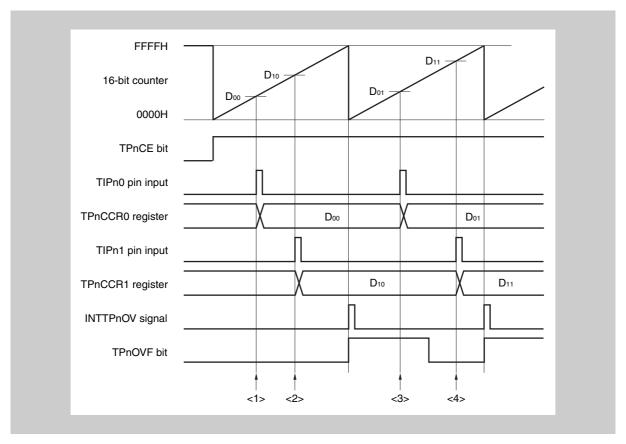

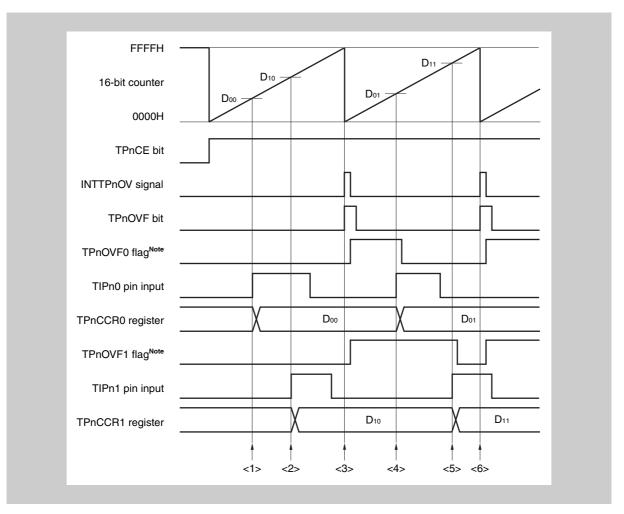

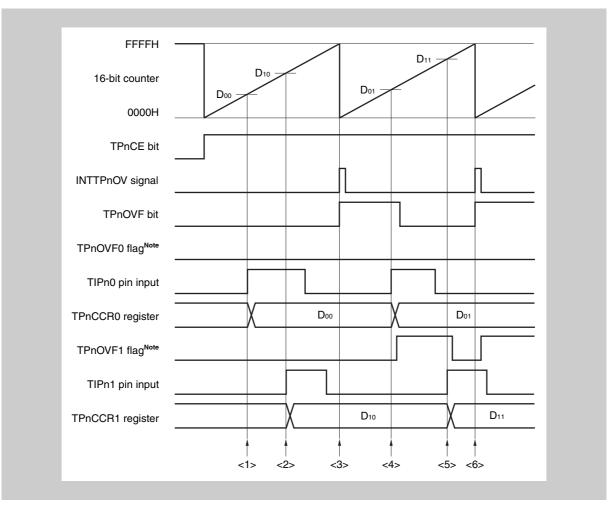

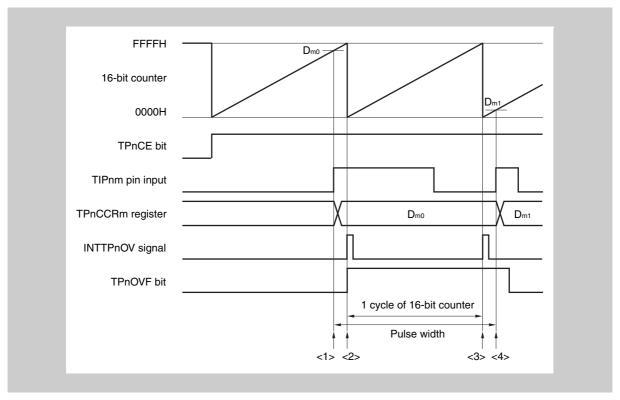

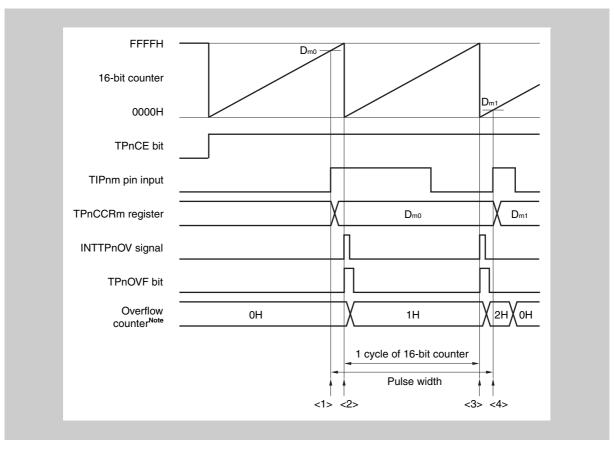

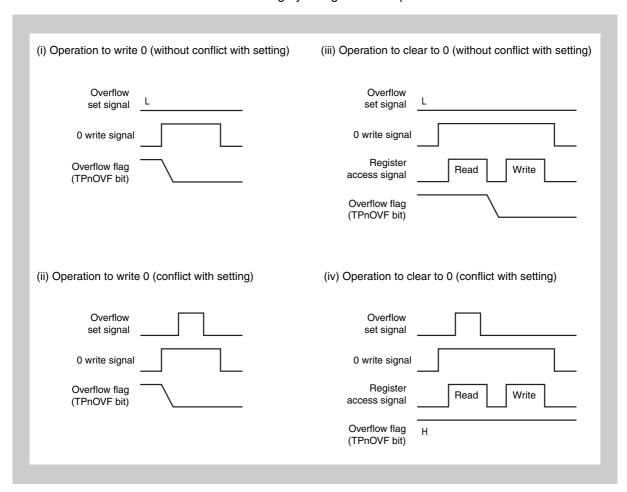

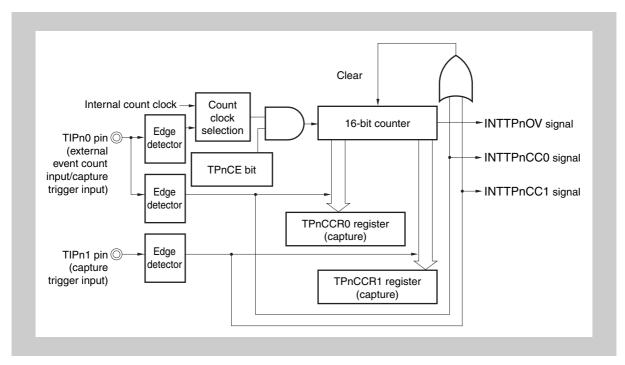

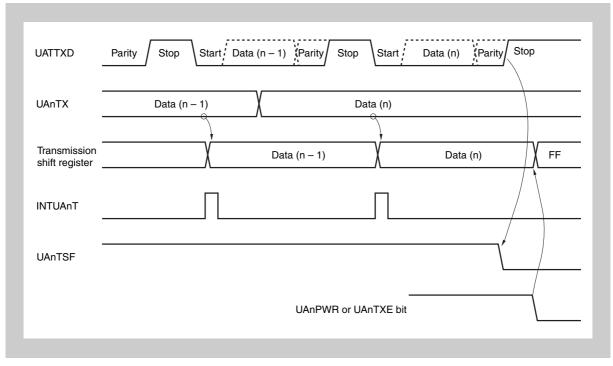

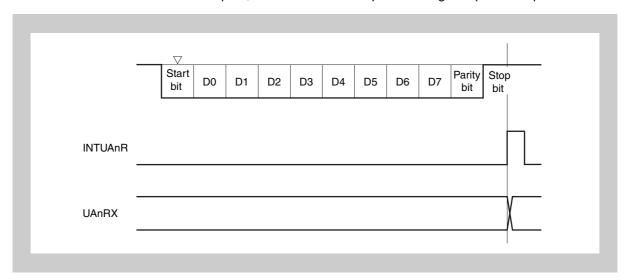

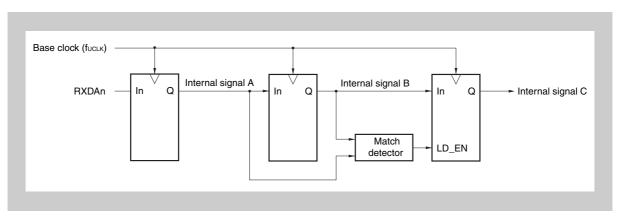

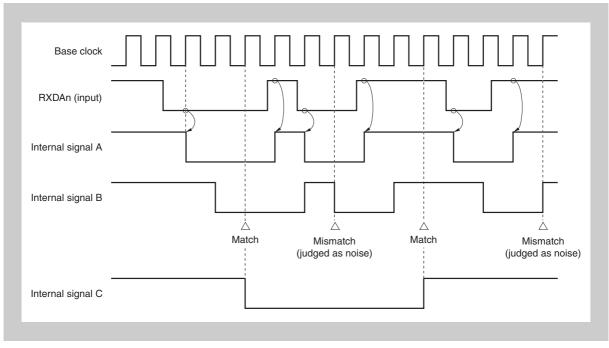

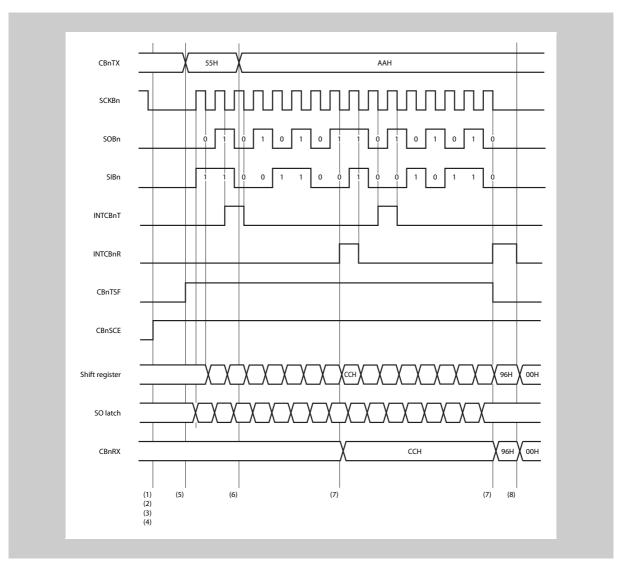

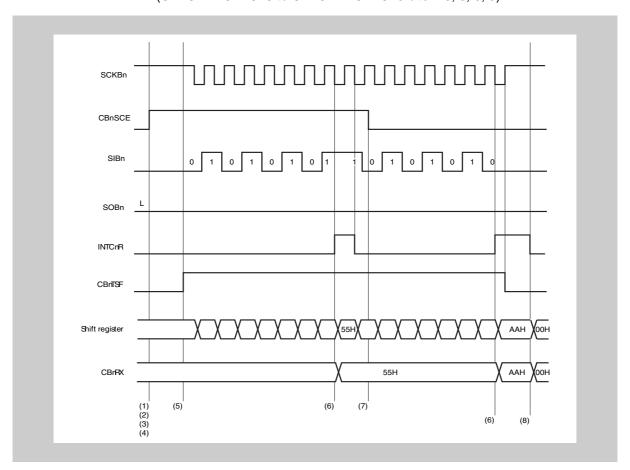

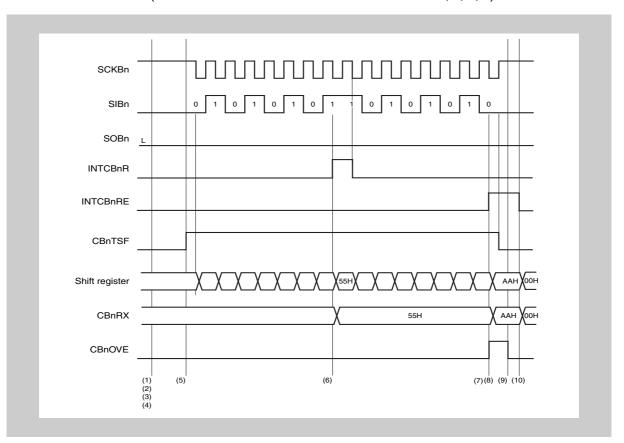

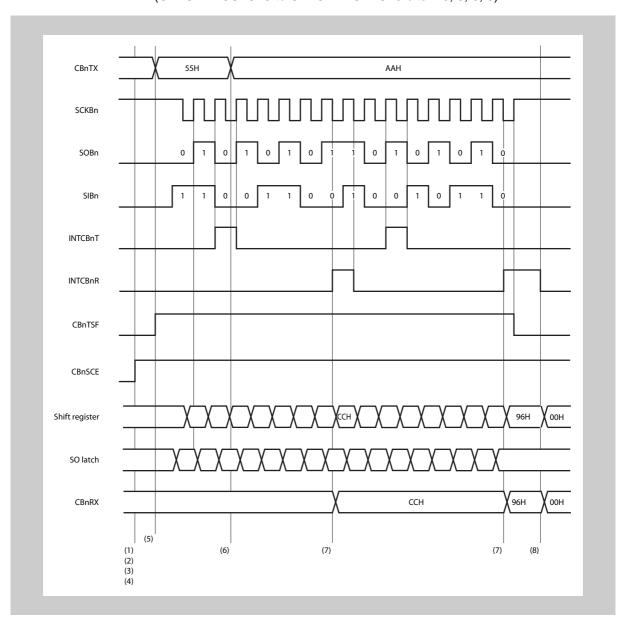

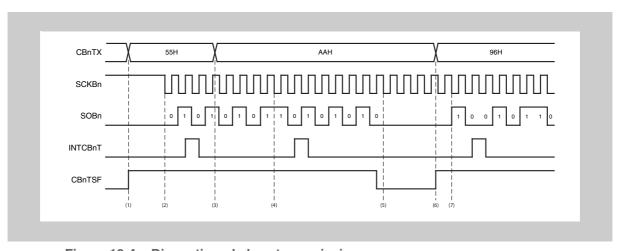

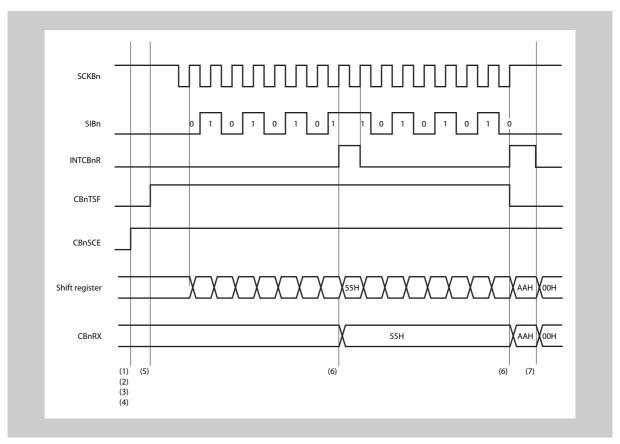

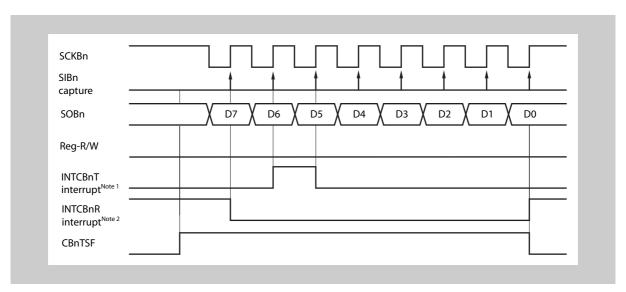

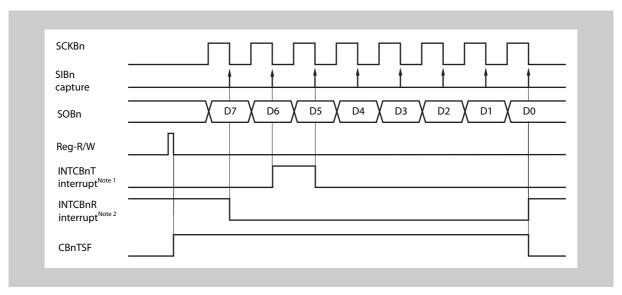

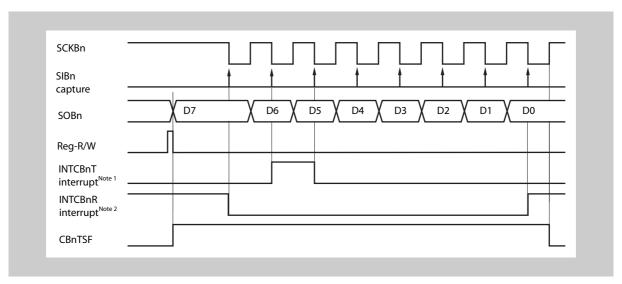

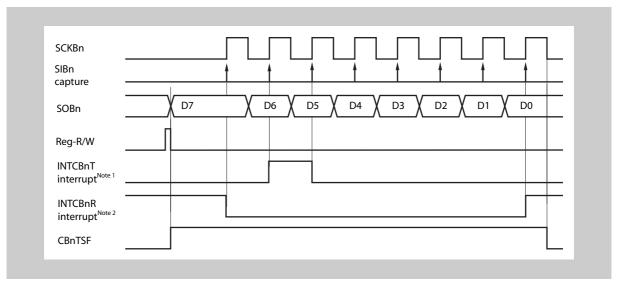

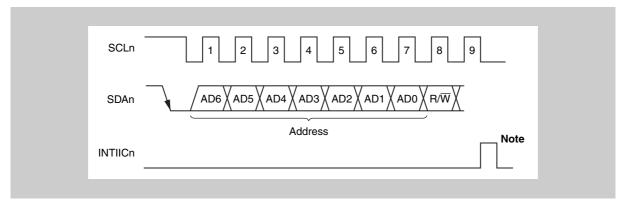

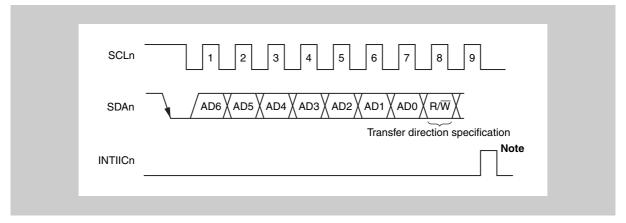

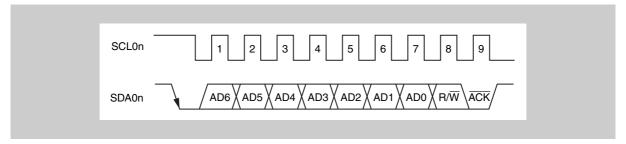

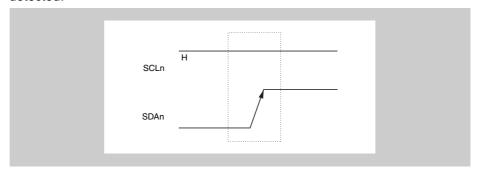

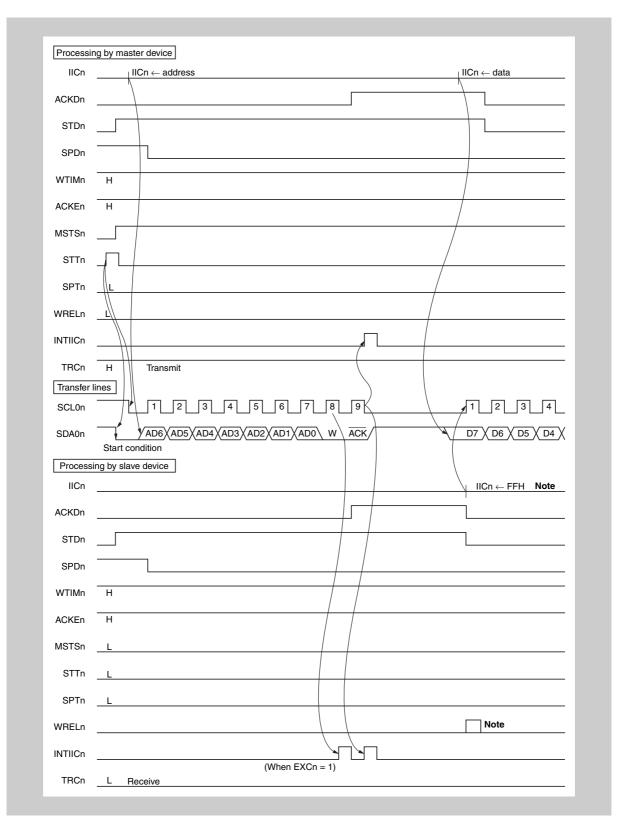

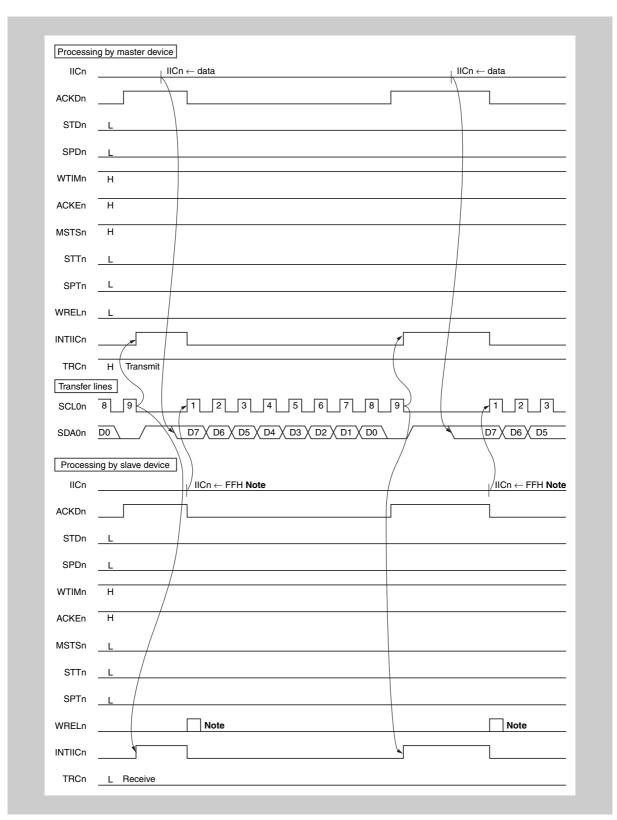

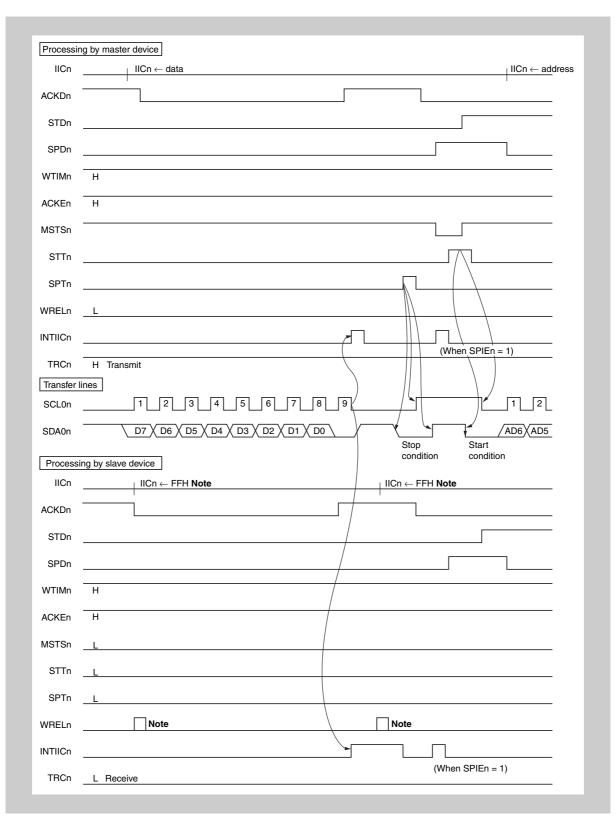

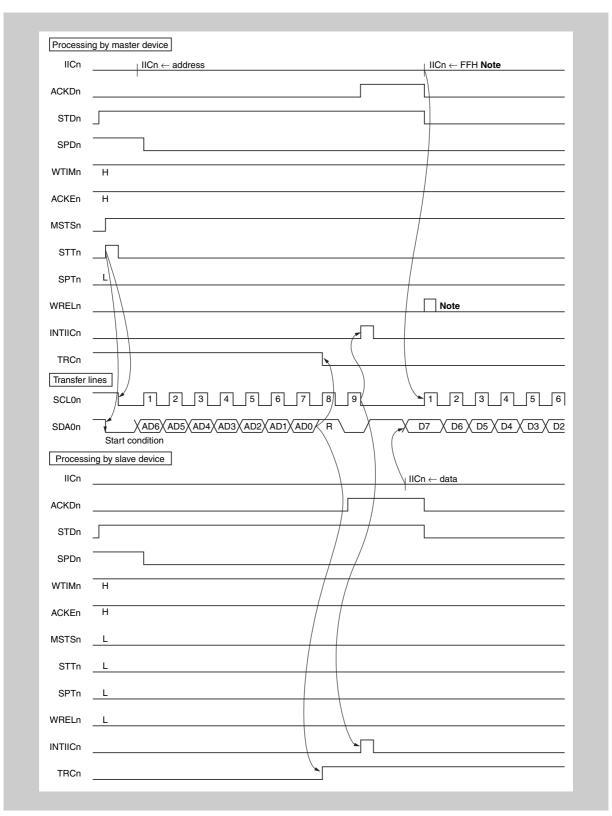

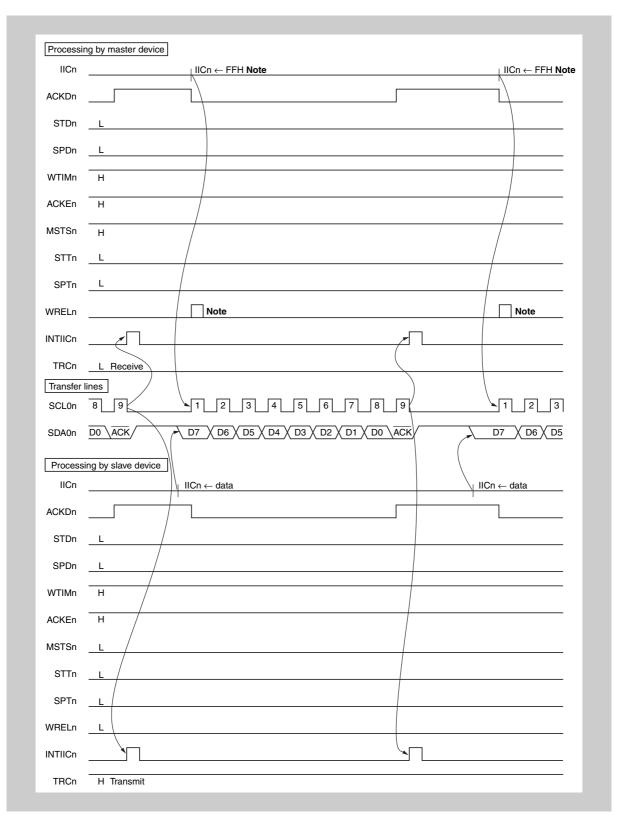

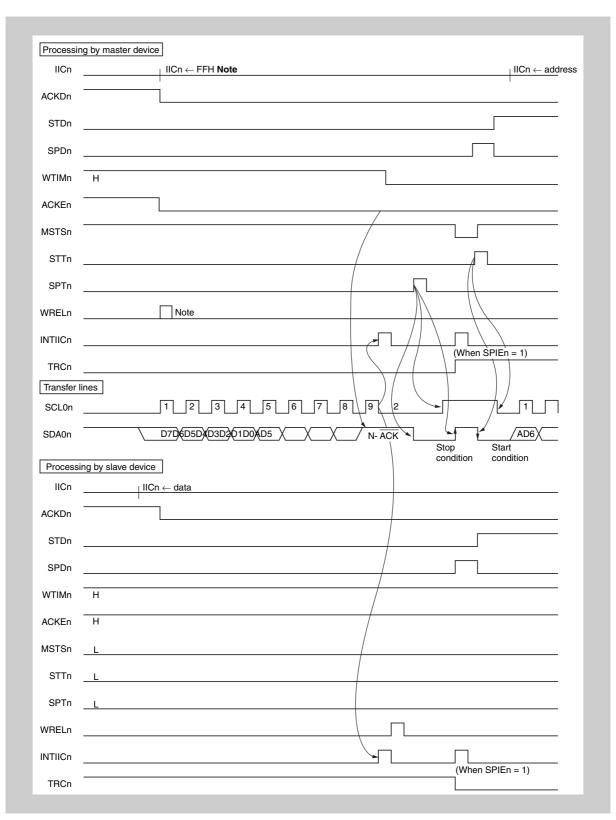

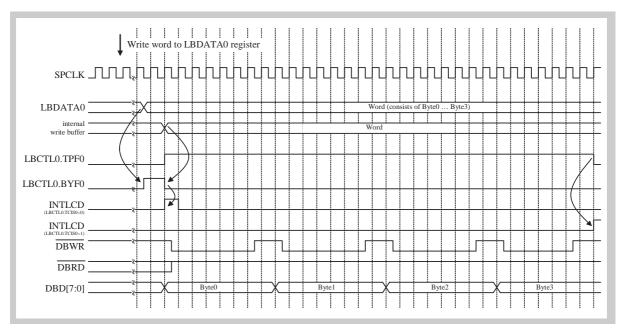

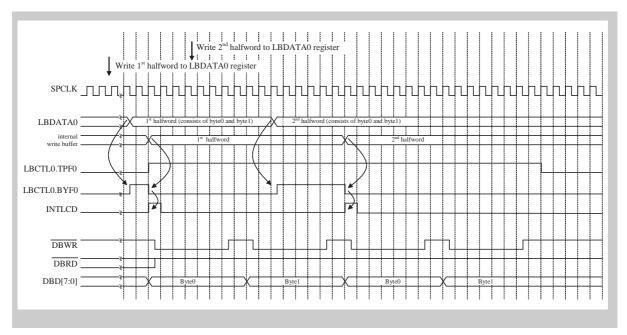

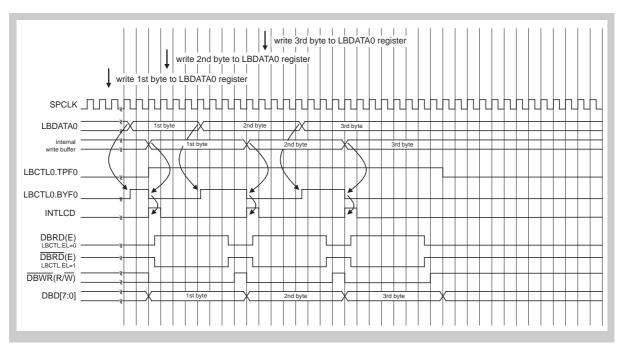

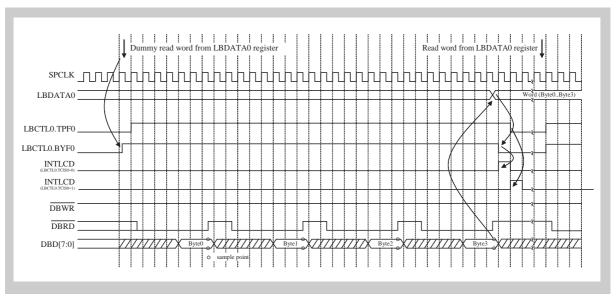

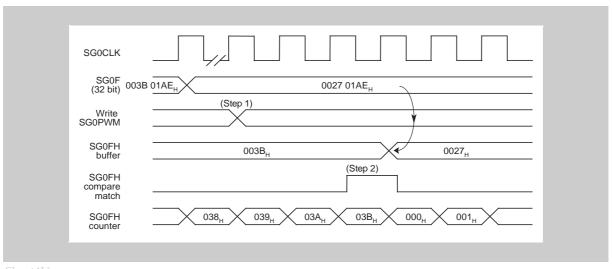

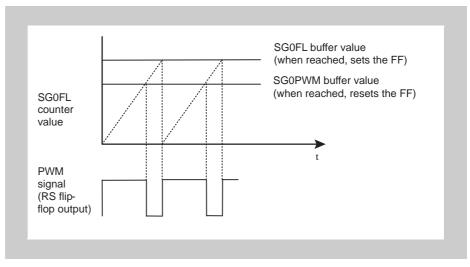

Timing diagrams are for functional explanation purposes only, without any

relevance to the real hardware implementation.

Further Information For further information see <a href="http://www.eu.necel.com">http://www.eu.necel.com</a>.

## **Table of Contents**

| Chap    | ter 1                                                                                                                                                                             | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 15                                                                                                       |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

|         | 1.1                                                                                                                                                                               | General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 15                                                                                                       |

|         | 1.2                                                                                                                                                                               | Features Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                          |

|         | 1.3                                                                                                                                                                               | Product Series Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                          |

|         |                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                          |

|         | 1.4                                                                                                                                                                               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 21                                                                                                       |

|         | 1.5                                                                                                                                                                               | Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 25                                                                                                       |

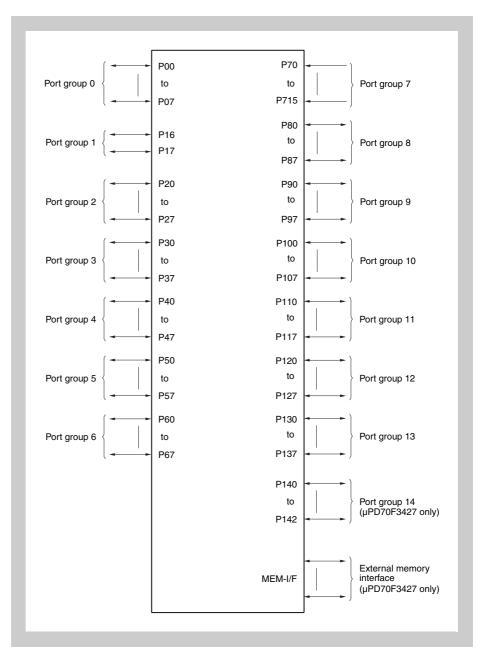

| Chap    | ter 2                                                                                                                                                                             | Pin Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 27                                                                                                       |

|         | 2.1                                                                                                                                                                               | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 27                                                                                                       |

|         | 2.1.1                                                                                                                                                                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 28                                                                                                       |

|         | 2.1.2                                                                                                                                                                             | Terms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 32                                                                                                       |

|         | 2.1.3                                                                                                                                                                             | Noise elimination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 32                                                                                                       |

|         | 2.2                                                                                                                                                                               | Port Group Configuration Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 33                                                                                                       |

|         | 2.2.1                                                                                                                                                                             | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                          |

|         | 2.2.2                                                                                                                                                                             | Pin function configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                          |

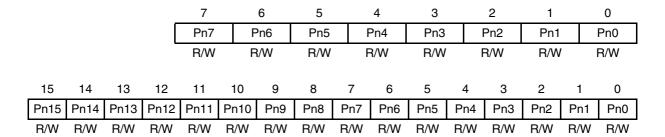

|         | 2.2.3                                                                                                                                                                             | Pin data input/output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 39                                                                                                       |

|         | 2.2.4                                                                                                                                                                             | Configuration of electrical characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 41                                                                                                       |

|         | 2.2.5                                                                                                                                                                             | Alternative input selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 44                                                                                                       |

|         | 2.3                                                                                                                                                                               | Port Types Diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 49                                                                                                       |

|         |                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _                                                                                                        |

|         | 2.4                                                                                                                                                                               | Port Group Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 54                                                                                                       |

|         | <b>2.4</b><br>2.4.1                                                                                                                                                               | Port Group Configuration  Port group configuration lists                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                          |

|         |                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 55                                                                                                       |

|         | 2.4.1                                                                                                                                                                             | Port group configuration lists                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 55<br>62                                                                                                 |

|         | 2.4.1<br>2.4.2                                                                                                                                                                    | Port group configuration lists                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 55<br>62<br>68                                                                                           |

|         | 2.4.1<br>2.4.2<br>2.4.3                                                                                                                                                           | Port group configuration lists                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 55<br>62<br>68<br>69                                                                                     |

|         | 2.4.1<br>2.4.2<br>2.4.3<br>2.4.4                                                                                                                                                  | Port group configuration lists                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 55<br>62<br>68<br>69<br>71                                                                               |

|         | 2.4.1<br>2.4.2<br>2.4.3<br>2.4.4<br>2.4.5                                                                                                                                         | Port group configuration lists.  Alphabetic pin function list.  External memory interface of µPD70F3427  Port group 0  Port group 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 55<br>62<br>68<br>69<br>71<br>72                                                                         |

|         | 2.4.1<br>2.4.2<br>2.4.3<br>2.4.4<br>2.4.5<br>2.4.6                                                                                                                                | Port group configuration lists.  Alphabetic pin function list.  External memory interface of µPD70F3427  Port group 0  Port group 1  Port group 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 55<br>62<br>68<br>69<br>71<br>72                                                                         |

|         | 2.4.1<br>2.4.2<br>2.4.3<br>2.4.4<br>2.4.5<br>2.4.6<br>2.4.7                                                                                                                       | Port group configuration lists.  Alphabetic pin function list.  External memory interface of µPD70F3427  Port group 0  Port group 1  Port group 2  Port group 3  Port group 4  Port group 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 55<br>62<br>68<br>71<br>72<br>74<br>76<br>78                                                             |

|         | 2.4.1<br>2.4.2<br>2.4.3<br>2.4.4<br>2.4.5<br>2.4.6<br>2.4.7<br>2.4.8                                                                                                              | Port group configuration lists.  Alphabetic pin function list.  External memory interface of µPD70F3427  Port group 0  Port group 1  Port group 2  Port group 3  Port group 4  Port group 5  Port group 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 55<br>62<br>68<br>69<br>71<br>72<br>74<br>76<br>78                                                       |

|         | 2.4.1<br>2.4.2<br>2.4.3<br>2.4.4<br>2.4.5<br>2.4.6<br>2.4.7<br>2.4.8<br>2.4.9                                                                                                     | Port group configuration lists.  Alphabetic pin function list.  External memory interface of µPD70F3427  Port group 0  Port group 1  Port group 2  Port group 3  Port group 4  Port group 5  Port group 6  Port group 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 55<br>62<br>68<br>69<br>71<br>72<br>74<br>76<br>80<br>82                                                 |

|         | 2.4.1<br>2.4.2<br>2.4.3<br>2.4.4<br>2.4.5<br>2.4.6<br>2.4.7<br>2.4.8<br>2.4.9<br>2.4.10<br>2.4.11<br>2.4.12                                                                       | Port group configuration lists.  Alphabetic pin function list.  External memory interface of µPD70F3427  Port group 0  Port group 1  Port group 2  Port group 3  Port group 4  Port group 5  Port group 6  Port group 7  Port group 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 55<br>62<br>68<br>71<br>72<br>74<br>76<br>80<br>82<br>84                                                 |

|         | 2.4.1<br>2.4.2<br>2.4.3<br>2.4.4<br>2.4.5<br>2.4.6<br>2.4.7<br>2.4.8<br>2.4.9<br>2.4.10<br>2.4.11<br>2.4.12<br>2.4.13                                                             | Port group configuration lists.  Alphabetic pin function list.  External memory interface of µPD70F3427  Port group 0  Port group 1  Port group 2  Port group 3  Port group 4  Port group 5  Port group 6  Port group 7  Port group 8  Port group 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 55<br>62<br>68<br>71<br>72<br>74<br>76<br>80<br>82<br>84<br>86                                           |

|         | 2.4.1<br>2.4.2<br>2.4.3<br>2.4.4<br>2.4.5<br>2.4.6<br>2.4.7<br>2.4.8<br>2.4.9<br>2.4.10<br>2.4.11<br>2.4.12<br>2.4.13<br>2.4.14                                                   | Port group configuration lists.  Alphabetic pin function list.  External memory interface of µPD70F3427  Port group 0  Port group 1  Port group 2  Port group 3  Port group 4  Port group 5  Port group 6  Port group 7  Port group 8  Port group 9  Port group 9  Port group 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 55<br>62<br>68<br>69<br>71<br>72<br>76<br>78<br>80<br>82<br>82<br>86<br>88                               |

|         | 2.4.1<br>2.4.2<br>2.4.3<br>2.4.4<br>2.4.5<br>2.4.6<br>2.4.7<br>2.4.8<br>2.4.9<br>2.4.10<br>2.4.11<br>2.4.12<br>2.4.13<br>2.4.14<br>2.4.15                                         | Port group configuration lists.  Alphabetic pin function list.  External memory interface of µPD70F3427  Port group 0  Port group 1  Port group 2  Port group 3  Port group 4  Port group 5  Port group 6  Port group 7  Port group 8  Port group 9  Port group 10  Port group 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 55<br>62<br>68<br>69<br>71<br>72<br>74<br>76<br>82<br>82<br>82<br>84<br>86<br>88<br>90                   |

| t4U.com | 2.4.1<br>2.4.2<br>2.4.3<br>2.4.4<br>2.4.5<br>2.4.6<br>2.4.7<br>2.4.8<br>2.4.9<br>2.4.10<br>2.4.11<br>2.4.12<br>2.4.13<br>2.4.14<br>2.4.15<br>2.4.16                               | Port group configuration lists.  Alphabetic pin function list.  External memory interface of µPD70F3427  Port group 0  Port group 1  Port group 2  Port group 3  Port group 4  Port group 5  Port group 6  Port group 7  Port group 8  Port group 9  Port group 10  Port group 11  Port group 12                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 55<br>62<br>68<br>69<br>71<br>72<br>74<br>76<br>80<br>82<br>84<br>86<br>88<br>90<br>92                   |

| t4U.com | 2.4.1<br>2.4.2<br>2.4.3<br>2.4.4<br>2.4.5<br>2.4.6<br>2.4.7<br>2.4.8<br>2.4.9<br>2.4.10<br>2.4.11<br>2.4.12<br>2.4.13<br>2.4.14<br>2.4.15<br>2.4.16<br>2.4.17                     | Port group configuration lists.  Alphabetic pin function list.  External memory interface of µPD70F3427  Port group 0  Port group 1  Port group 2  Port group 3  Port group 4  Port group 5  Port group 6  Port group 7  Port group 8  Port group 9  Port group 10  Port group 11  Port group 12  Port group 13                                                                                                                                                                                                                                                                                                                                                                                                                                     | 55<br>62<br>68<br>71<br>72<br>74<br>76<br>82<br>82<br>84<br>86<br>88<br>90<br>92                         |

| 4U.com  | 2.4.1<br>2.4.2<br>2.4.3<br>2.4.4<br>2.4.5<br>2.4.6<br>2.4.7<br>2.4.8<br>2.4.9<br>2.4.10<br>2.4.11<br>2.4.12<br>2.4.13<br>2.4.14<br>2.4.15<br>2.4.16<br>2.4.17<br>2.4.18           | Port group configuration lists.  Alphabetic pin function list.  External memory interface of µPD70F3427  Port group 0  Port group 1  Port group 2  Port group 3  Port group 4  Port group 5  Port group 6  Port group 7  Port group 8  Port group 9  Port group 10  Port group 11  Port group 12  Port group 13  Port group 14  Port group 14  Port group 15  Port group 11  Port group 14  Port group 14 | 55<br>62<br>68<br>71<br>72<br>74<br>76<br>82<br>82<br>84<br>86<br>88<br>92<br>92<br>92                   |

| t4U.com | 2.4.1<br>2.4.2<br>2.4.3<br>2.4.4<br>2.4.5<br>2.4.6<br>2.4.7<br>2.4.8<br>2.4.9<br>2.4.10<br>2.4.11<br>2.4.12<br>2.4.13<br>2.4.14<br>2.4.15<br>2.4.16<br>2.4.17<br>2.4.18<br>2.4.19 | Port group configuration lists.  Alphabetic pin function list.  External memory interface of µPD70F3427  Port group 0  Port group 1  Port group 2  Port group 3  Port group 4  Port group 5  Port group 6  Port group 7  Port group 8  Port group 9  Port group 10  Port group 11  Port group 12  Port group 13  Port group 14  Port group 13  Port group 14  Port group 15  Port group 17  Port group 19  Port group 10  Port group 11  Port group 11  Port group 13  Port group 14 (µPD70F3427 only)  Port group AL                                                                                                                                                                                                                               | 55<br>62<br>68<br>71<br>72<br>74<br>76<br>80<br>82<br>84<br>86<br>82<br>90<br>92<br>93<br>94             |

| t4U.com | 2.4.1<br>2.4.2<br>2.4.3<br>2.4.4<br>2.4.5<br>2.4.6<br>2.4.7<br>2.4.8<br>2.4.9<br>2.4.10<br>2.4.11<br>2.4.12<br>2.4.13<br>2.4.14<br>2.4.15<br>2.4.16<br>2.4.17<br>2.4.18           | Port group configuration lists.  Alphabetic pin function list.  External memory interface of µPD70F3427  Port group 0  Port group 1  Port group 2  Port group 3  Port group 4  Port group 5  Port group 6  Port group 7  Port group 8  Port group 9  Port group 10  Port group 11  Port group 12  Port group 13  Port group 14  Port group 14  Port group 15  Port group 11  Port group 14  Port group 14 | 55<br>62<br>68<br>69<br>71<br>72<br>76<br>80<br>82<br>82<br>82<br>82<br>82<br>92<br>92<br>93<br>94<br>95 |

www.batabileet40.com

|                  | 2.4.22 | Port group CT                                | 99  |

|------------------|--------|----------------------------------------------|-----|

|                  | 2.4.23 | Port group DL                                | 100 |

|                  | 2.4.24 | Port group DH                                | 102 |

|                  | 2.5    | Noise Elimination                            | 104 |

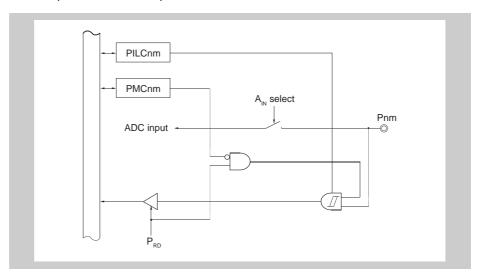

|                  | 2.5.1  | Analog filtered inputs                       | 104 |

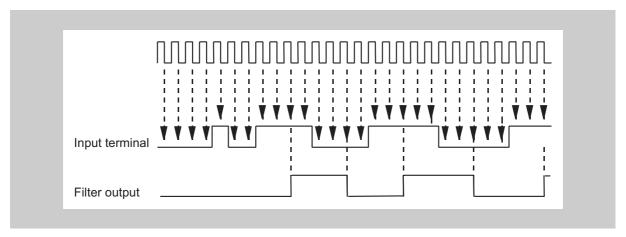

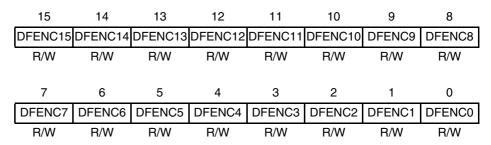

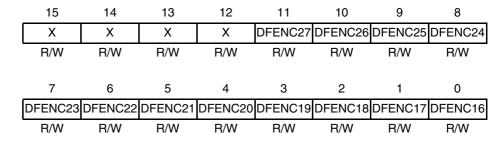

|                  | 2.5.2  | Digitally filtered inputs                    | 104 |

|                  | 2.6    | Pin Functions in Reset and Power Save Modes  | 108 |

|                  | 2.7    | Recommended Connection of unused Pins        | 109 |

|                  | 2.8    | Package Pins Assignment                      | 110 |

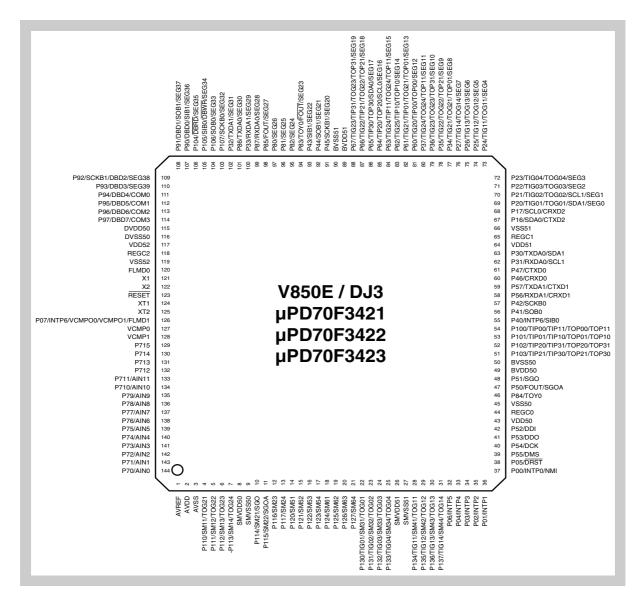

|                  | 2.8.1  | μPD70F3421, μPD70F3422, μPD70F3423           | 110 |

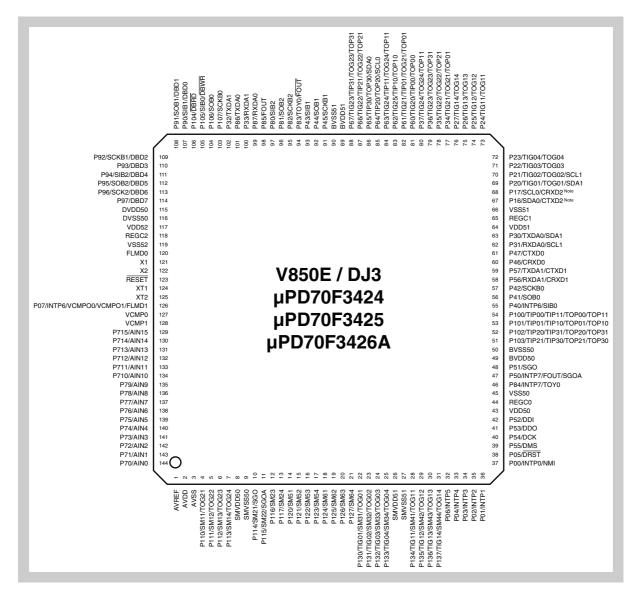

|                  | 2.8.2  | μPD70F3424, μPD70F3425, μPD70F3426A          | 111 |

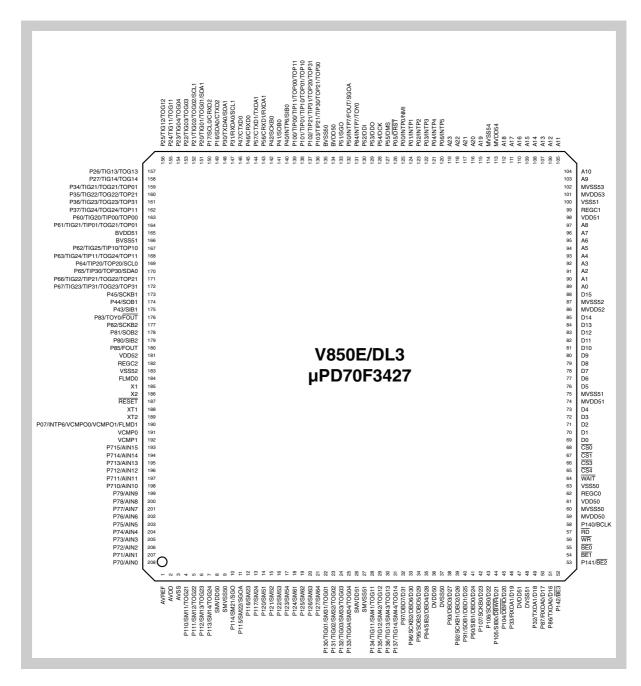

|                  | 2.8.3  | μPD70F3427                                   | 112 |

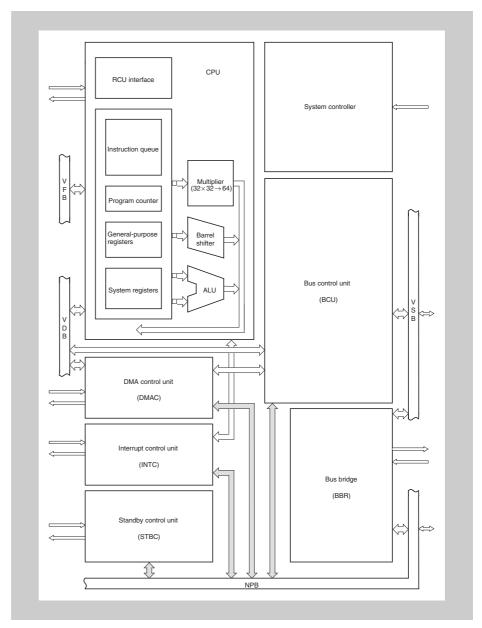

| Cha              | pter 3 | CPU System Functions                         | 113 |

| •                | 3.1    | Overview                                     |     |

|                  | 3.1.1  | Description                                  |     |

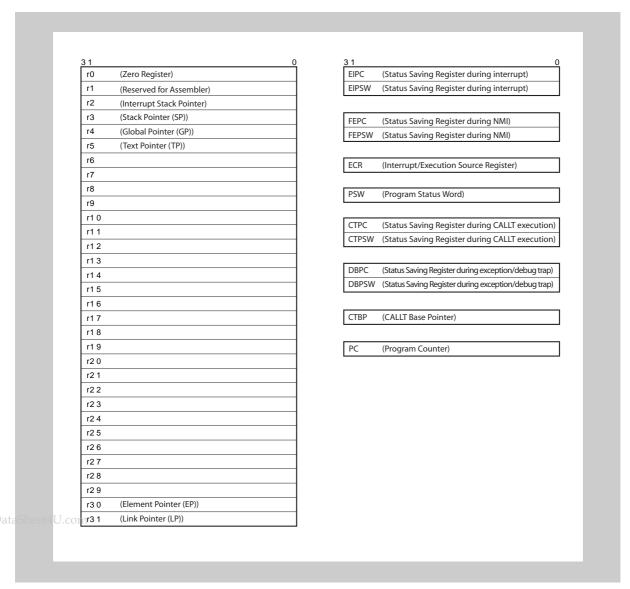

|                  | 3.2    | CPU Register Set                             | 115 |

|                  | 3.2.1  | General purpose registers (r0 to r31)        |     |

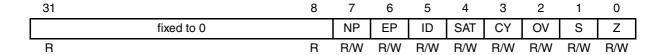

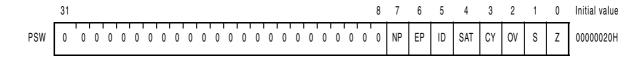

|                  | 3.2.2  | System register set                          |     |

|                  | 3.3    | Operation Modes                              | 125 |

|                  | 3.3.1  | Normal operation mode                        | 125 |

|                  | 3.3.2  | Flash programming mode                       | 126 |

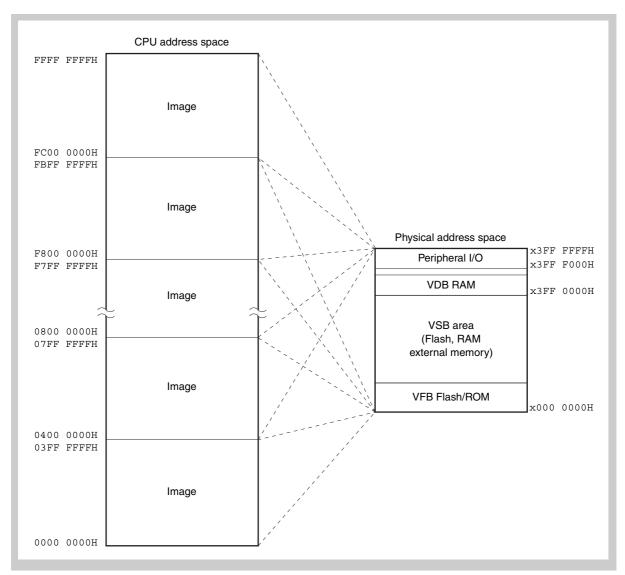

|                  | 3.4    | Address Space                                | 126 |

|                  | 3.4.1  | CPU address space and physical address space | 126 |

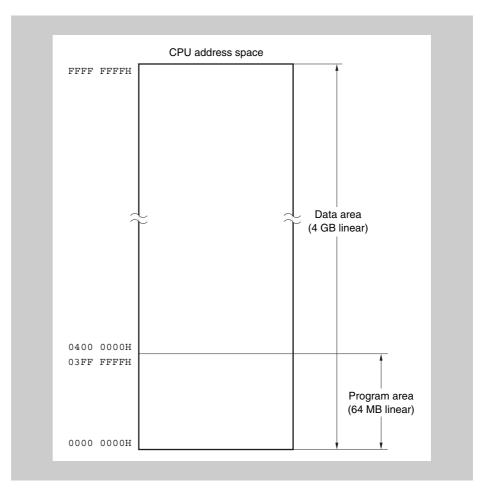

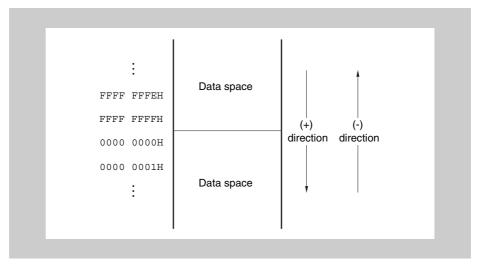

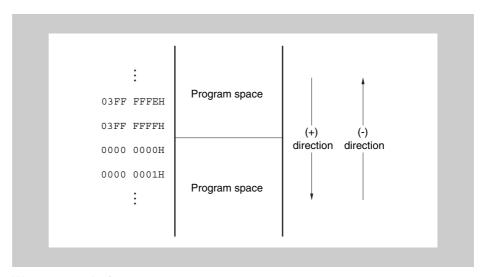

|                  | 3.4.2  | Program and data space                       | 128 |

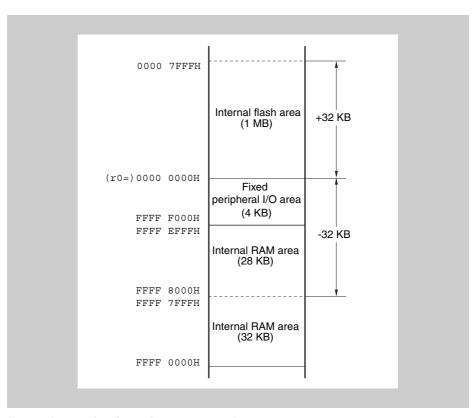

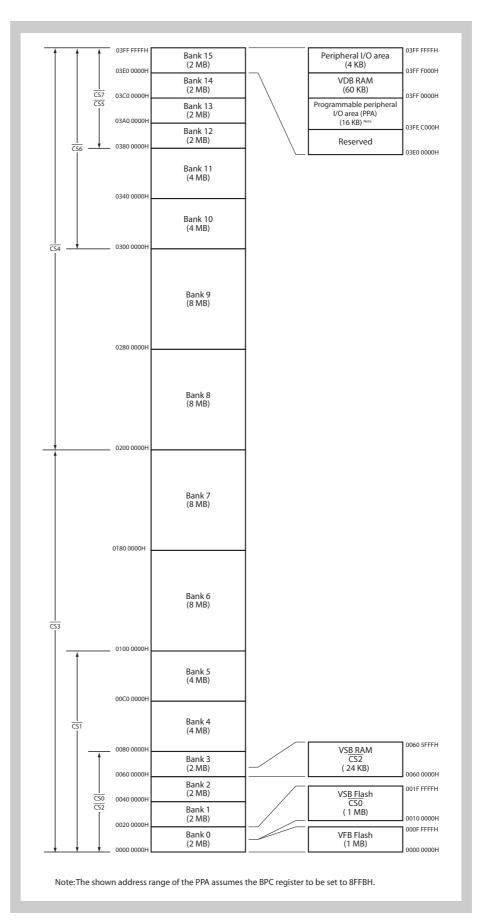

|                  | 3.5    | Memory                                       | 130 |

|                  | 3.5.1  | Memory areas                                 | 130 |

|                  | 3.5.2  | Fixed peripheral I/O area                    | 132 |

|                  | 3.5.3  | Recommended use of data address space        | 134 |

|                  | 3.6    | Write Protected Registers                    | 135 |

|                  | 3.7    | Instructions and Data Access Times           | 136 |

| Cha <sub>l</sub> | pter 4 | Clock Generator                              | 139 |

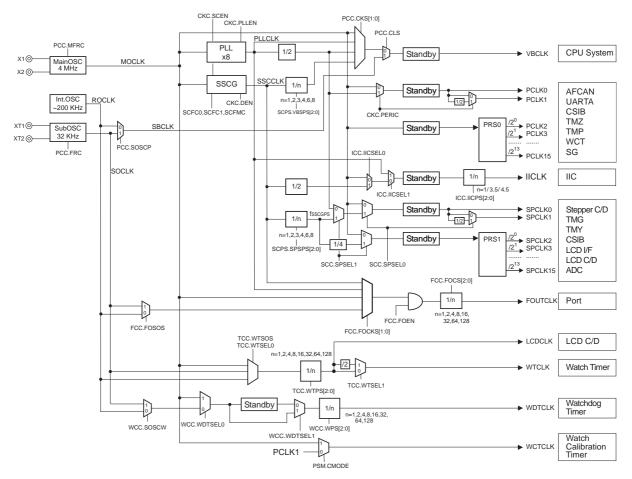

|                  | 4.1    | Overview                                     | 139 |

|                  | 4.1.1  | Description                                  | 140 |

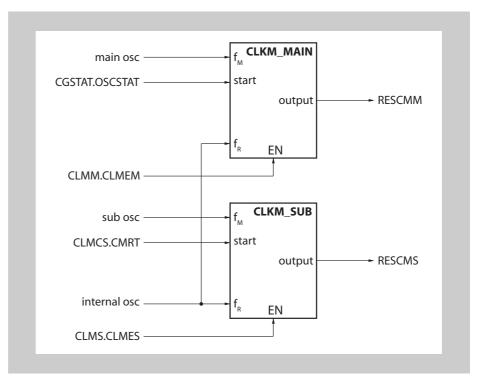

|                  | 4.1.2  | Clock monitors                               | 142 |

| Sheet4U.com      | 4.1.3  | Power save modes overview                    | 143 |

| nicet#U.COIII    | 4.1.4  | Start conditions                             |     |

|                  | 4.1.5  | Start-up guideline                           | 145 |

|                  | 4.2    | Clock Generator Registers                    | 146 |

|                  | 4.2.1  | General clock generator registers            | 148 |

|                  | 4.2.2  | SSCG control registers                       | 155 |

|        | 4.2.3          | Control registers for peripheral clocks        | 161 |

|--------|----------------|------------------------------------------------|-----|

|        | 4.2.4          | Control registers for power save modes         | 169 |

|        | 4.2.5          | Clock monitor registers                        | 175 |

|        | 4.3            | Power Save Modes                               | 179 |

|        | 4.3.1          | Power save modes description                   | 179 |

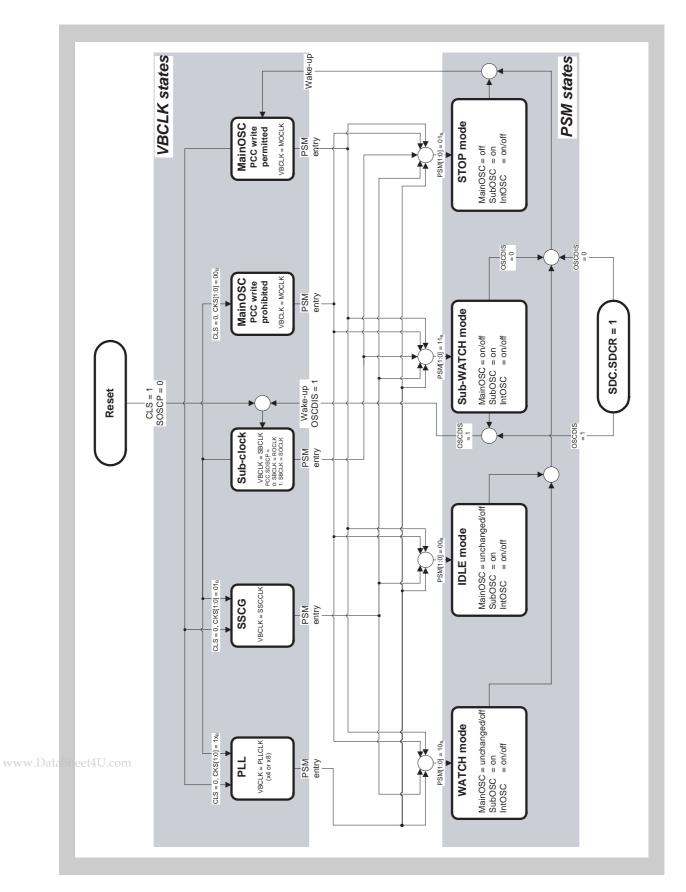

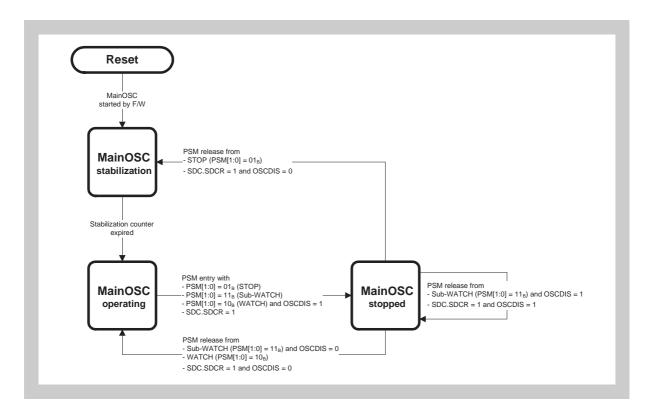

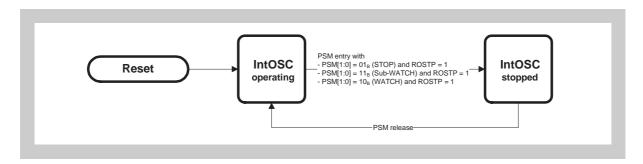

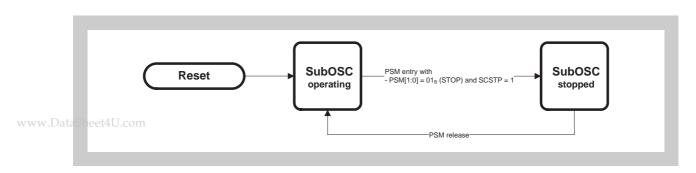

|        | 4.3.2          | Clock Generator state transitions              |     |

|        | 4.3.3          | Power save mode activation                     |     |

|        | 4.3.4          | CPU operation after power save mode release    |     |

|        | 4.4            | Clock Generator Operation                      |     |

|        | 4.4.1          | Internal and sub oscillator operation          |     |

|        | 4.4.2          | Watch Timer and Watch Calibration Timer clocks |     |

|        | 4.4.3<br>4.4.4 | Clock output FOUTCLK                           |     |

|        | 4.4.4          | Default clock generator setup                  |     |

|        | 4.4.5          | Operation of the Clock Monitors                | 190 |

| Chap   | oter 5         | Interrupt Controller (INTC)                    | 201 |

|        | 5.1            | Features                                       | 201 |

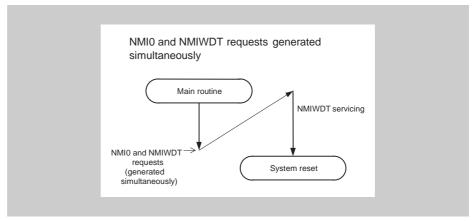

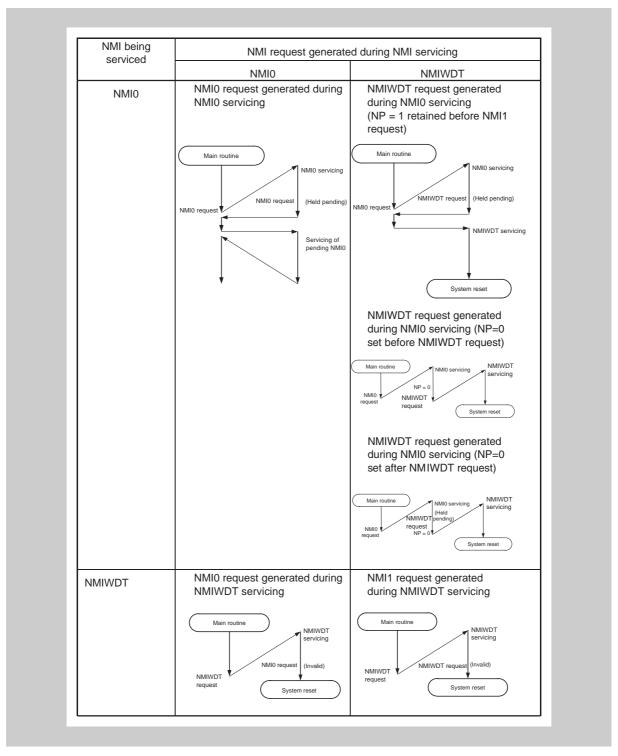

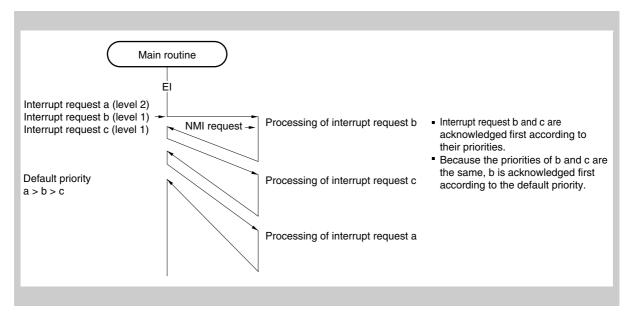

|        | 5.2            | Non-Maskable Interrupts                        | 226 |

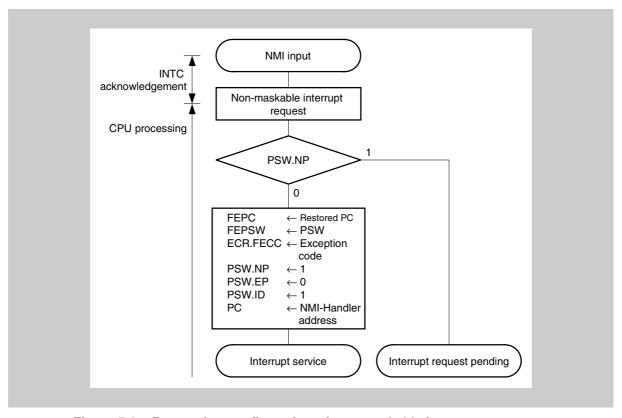

|        | 5.2.1          | Operation                                      | 229 |

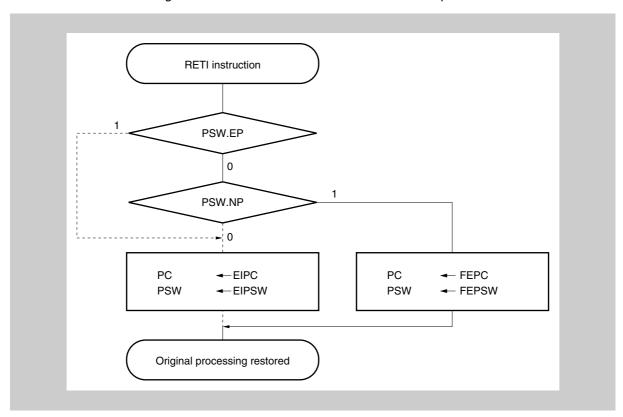

|        | 5.2.2          | Restore                                        |     |

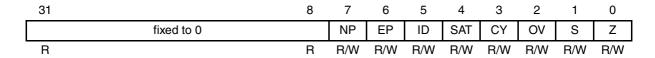

|        | 5.2.3          | Non-maskable interrupt status flag (NP)        |     |

|        | 5.2.4          | NMI0 control                                   | 231 |

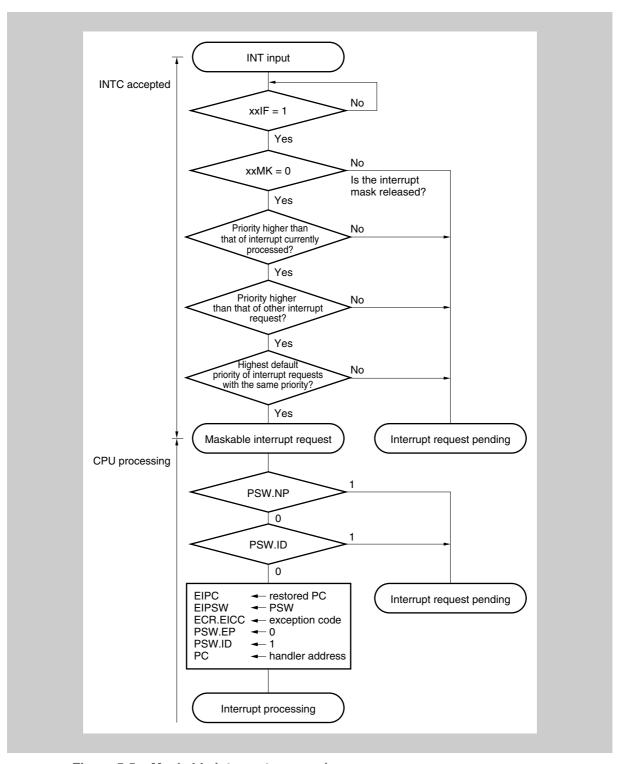

|        | 5.3            | Maskable Interrupts                            |     |

|        | 5.3.1          | Operation                                      |     |

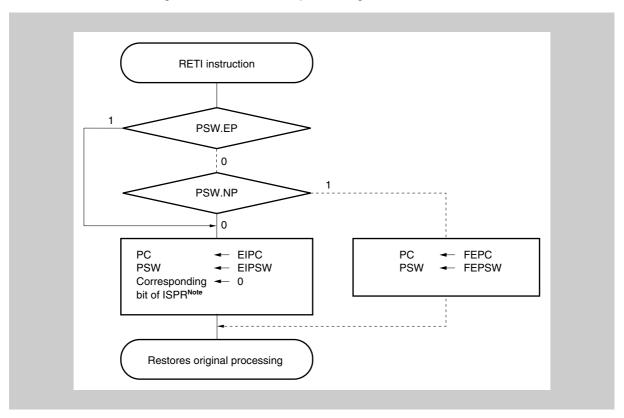

|        | 5.3.2          | Restore                                        |     |

|        | 5.3.3          | Priorities of maskable interrupts              |     |

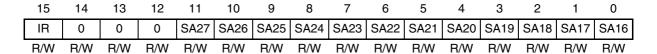

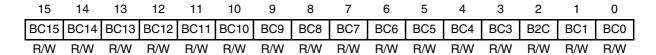

|        | 5.3.4<br>5.3.5 | xxIC - Maskable interrupts control register    |     |

|        | 5.3.6          | ISPR - In-service priority register            |     |

|        | 5.3.7          | Maskable interrupt status flag (ID)            |     |

|        | 5.3.8          | External maskable interrupts                   |     |

|        | 5.3.9          | Software interrupts                            |     |

|        | 5.4            | Edge and Level Detection Configuration         | 257 |

|        | 5.5            | Software Exception                             | 259 |

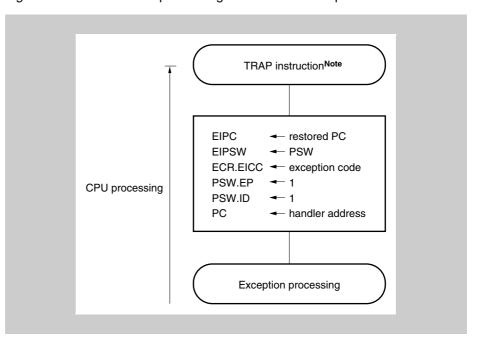

|        | 5.5.1          | Operation                                      | 259 |

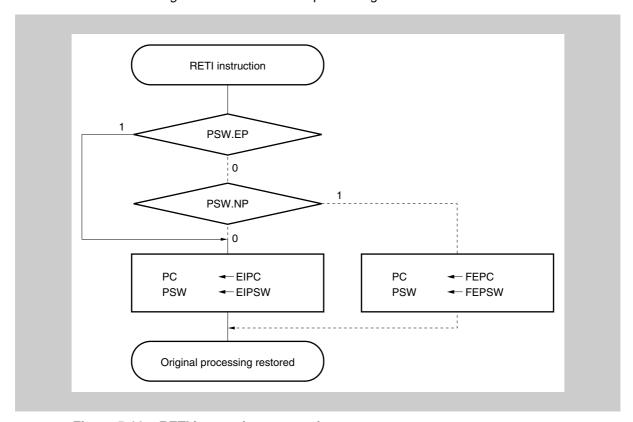

|        | 5.5.2          | Restore                                        | 260 |

|        | 5.5.3          | Exception status flag (EP)                     | 261 |

|        | 5.6            | Exception Trap                                 | 261 |

| 4U.com | 5.6.1          | Illegal opcode definition                      | 261 |

|        | 5.6.2          | Debug trap                                     | 263 |

|        | 0.0.2          |                                                |     |

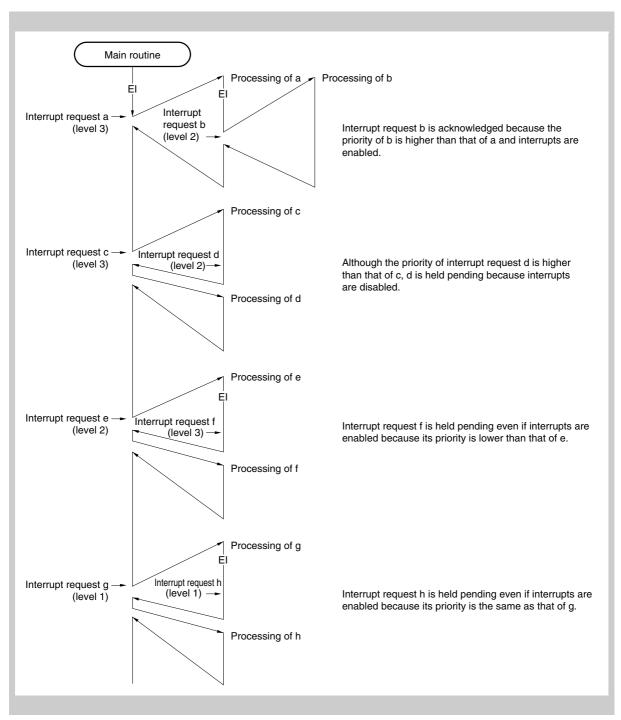

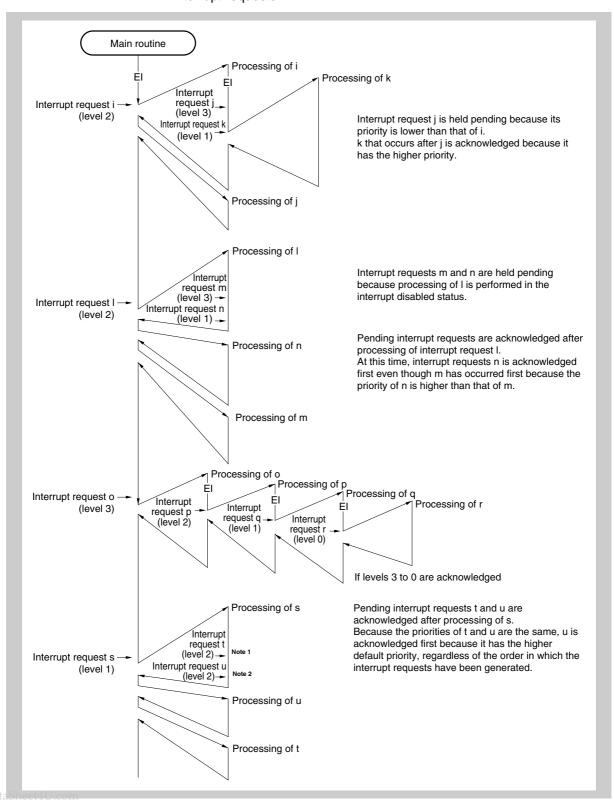

|        | 5.7            | Multiple Interrupt Processing Control          | 264 |

|        |                | Multiple Interrupt Processing Control          |     |

User's Manual U17566EE5V1UM00

| Chapter 6            | Flash Memory                                                        | 269   |

|----------------------|---------------------------------------------------------------------|-------|

| 6.1                  | Overview                                                            | 270   |

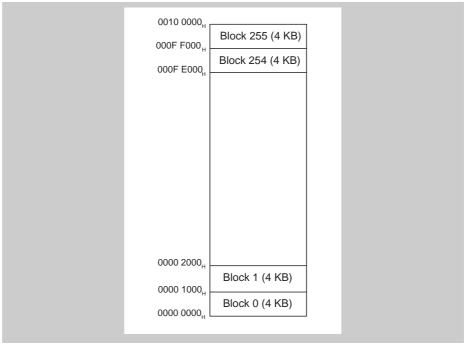

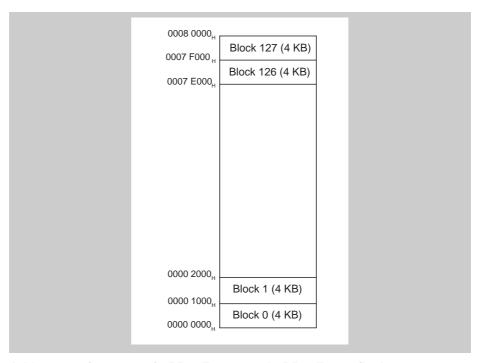

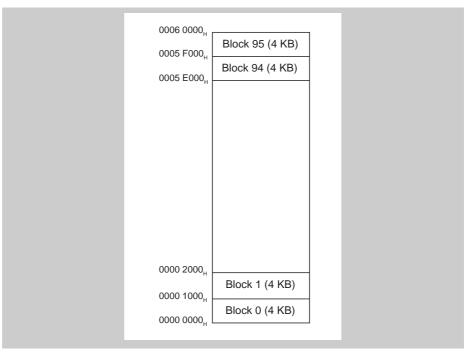

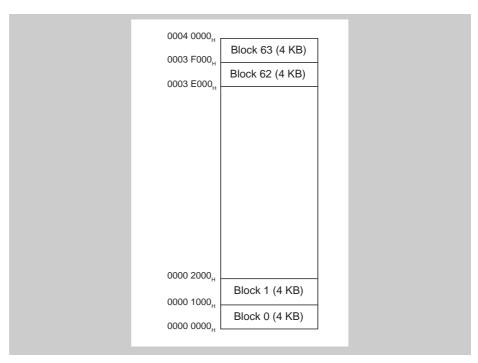

| 6.1.1                | Flash memory address assignment                                     | 271   |

| 6.1.2                | Flash memory erasure and rewrite                                    | . 273 |

| 6.1.3                | Flash memory programming                                            | 274   |

| 6.1.4                | Boot block swapping                                                 | 274   |

| 6.2                  | Flash Self-Programming                                              | . 275 |

| 6.2.1                | Flash self-programming registers                                    | 275   |

| 6.2.2                | Interrupt handling during flash self-programming                    | . 277 |

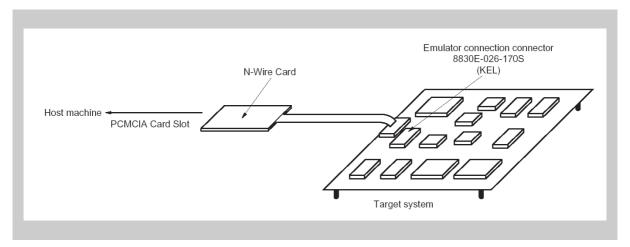

| 6.3                  | Flash Programming via N-Wire                                        | . 278 |

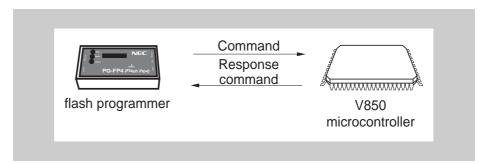

| 6.4                  | Flash Programming with Flash Programmer                             | . 279 |

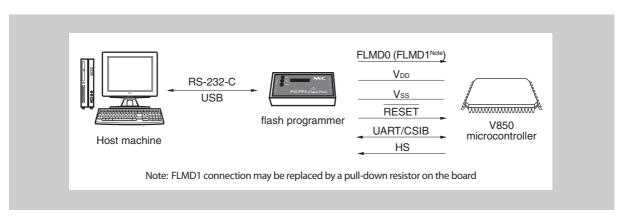

| 6.4.1                | Programming environment                                             | 279   |

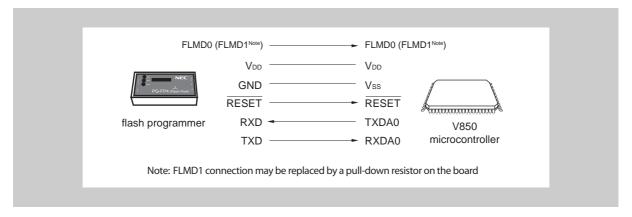

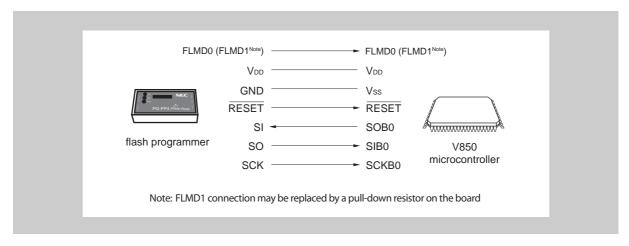

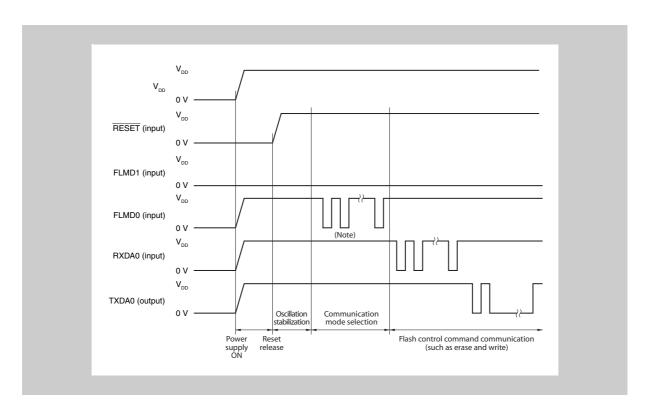

| 6.4.2                | Communication mode                                                  | . 280 |

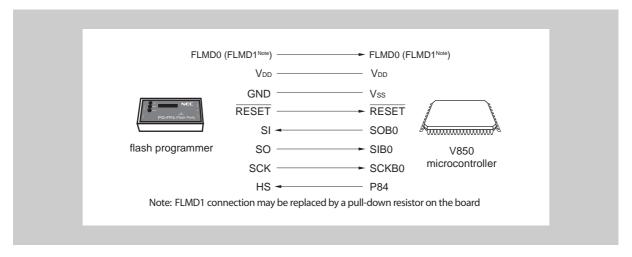

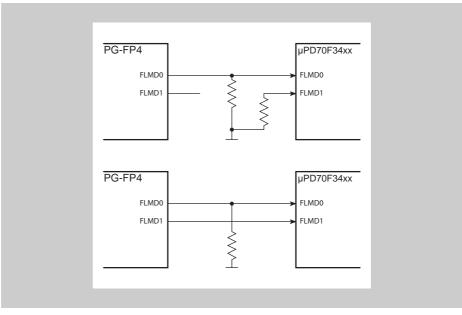

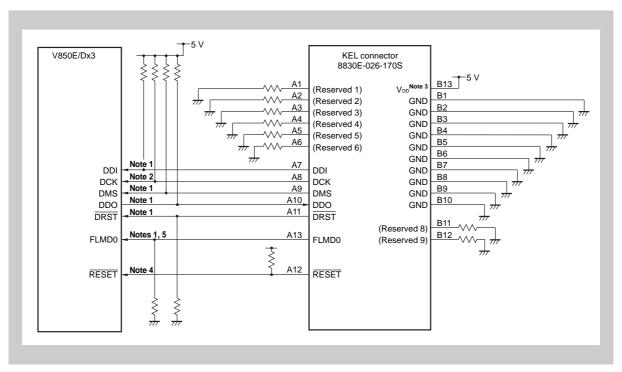

| 6.4.3                | Pin connection                                                      |       |

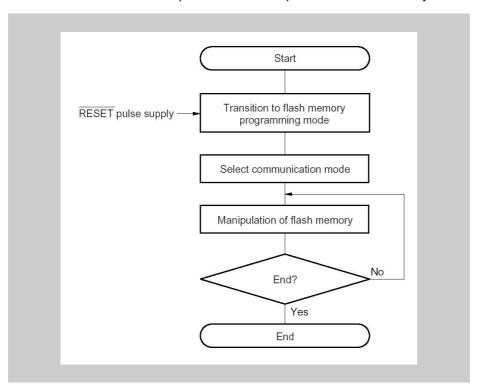

| 6.4.4                | Programming method                                                  | 285   |

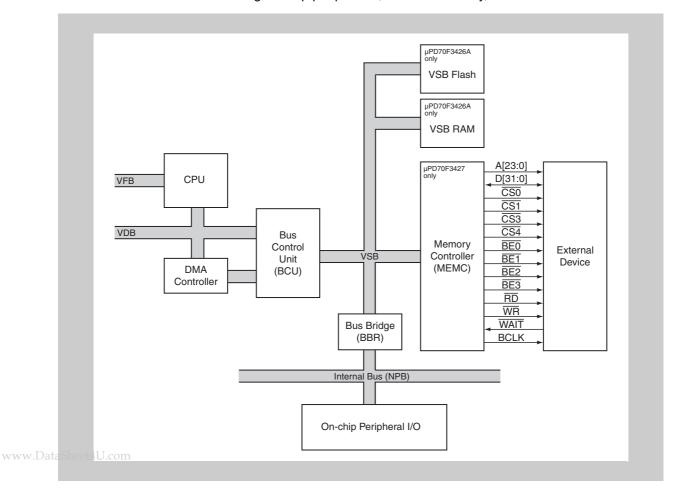

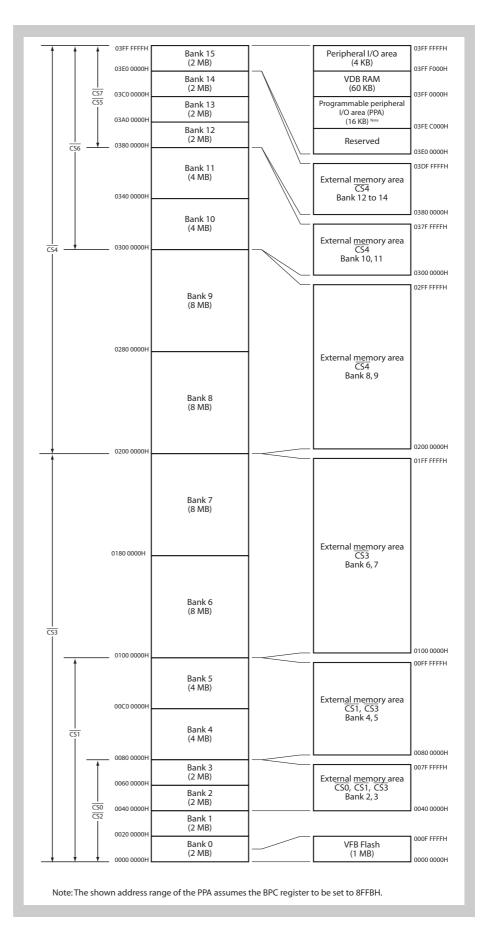

| Chapter 7            | Bus and Memory Control (BCU, MEMC)                                  | . 289 |

| 7.1                  | Overview                                                            | . 289 |

| 7.2                  | Description                                                         | . 290 |

| 7.2.1                | Memory banks and chip select signals                                | . 292 |

| 7.2.2                | Chips select priority control                                       | 295   |

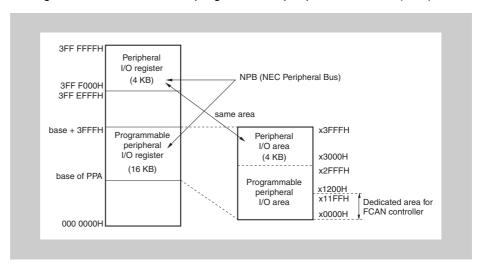

| 7.2.3                | Peripheral I/O area                                                 | . 295 |

| 7.2.4                | NPB access timing                                                   |       |

| 7.2.5                | Bus properties                                                      |       |

| 7.2.6                | Boundary operation conditions                                       |       |

| 7.2.7                | Initialization for access to external devices                       |       |

| 7.2.8                | External bus mute function                                          |       |

| 7.3                  | 5                                                                   |       |

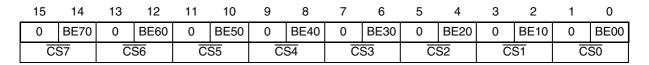

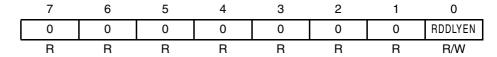

| 7.3.1                | BCU registers                                                       |       |

| 7.3.2                | Memory controller registers (μPD70F3427 only)                       | 311   |

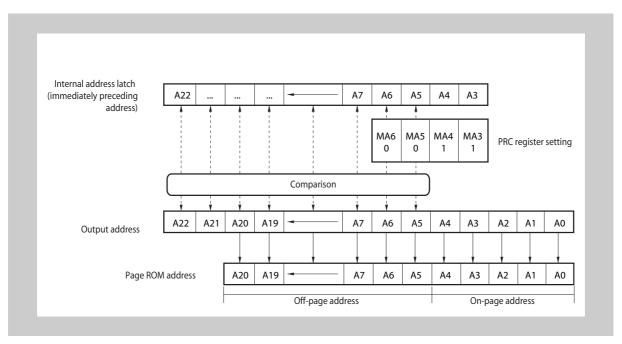

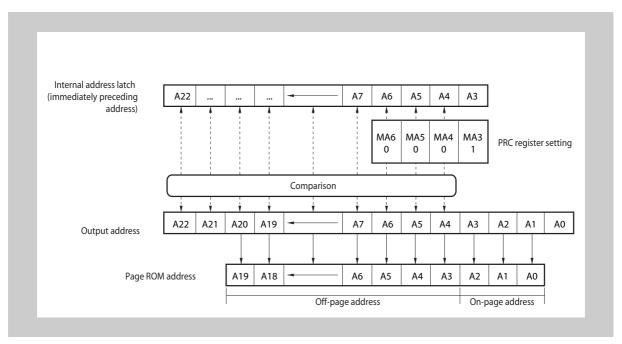

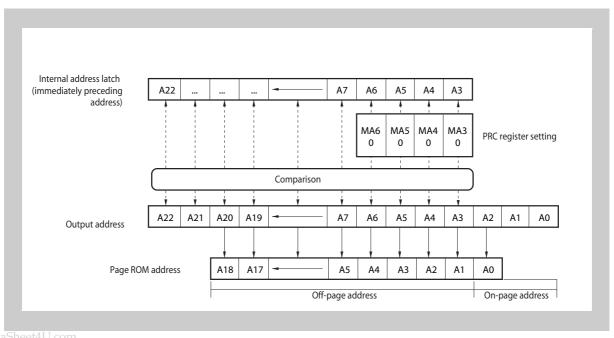

| 7.4                  | Page ROM Controller                                                 | 320   |

| 7.5                  | Configuration of Memory Access                                      | . 322 |

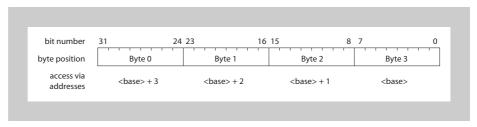

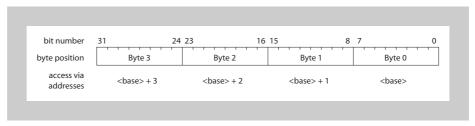

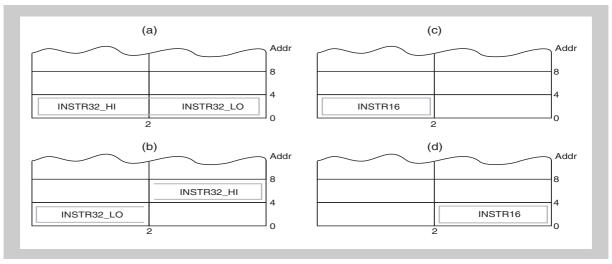

| 7.5.1                | Endian format                                                       |       |

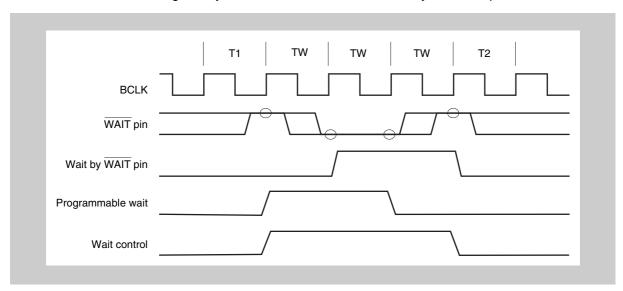

| 7.5.2                | Wait function                                                       |       |

| 7.5.3                | Idle state insertion                                                | 324   |

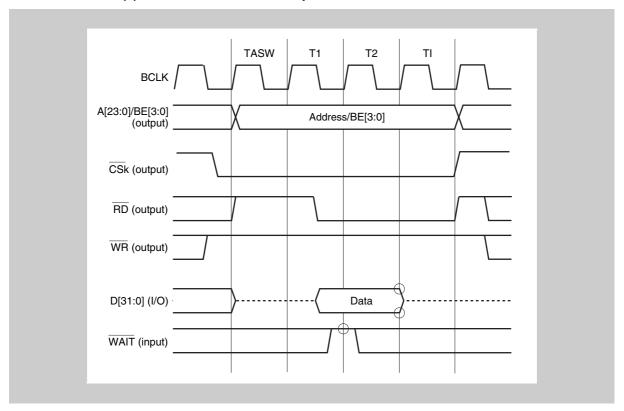

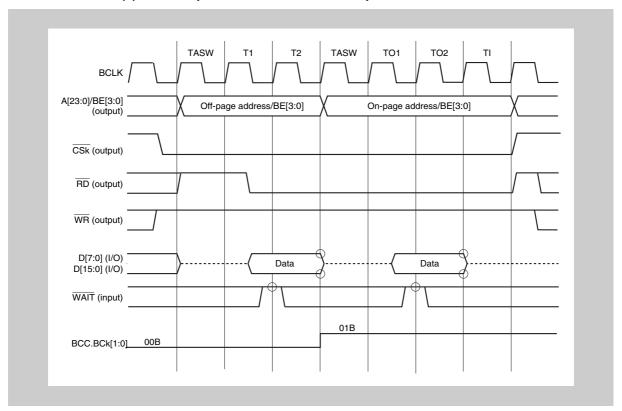

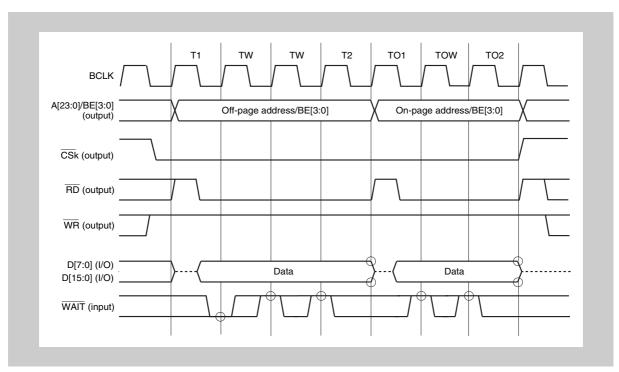

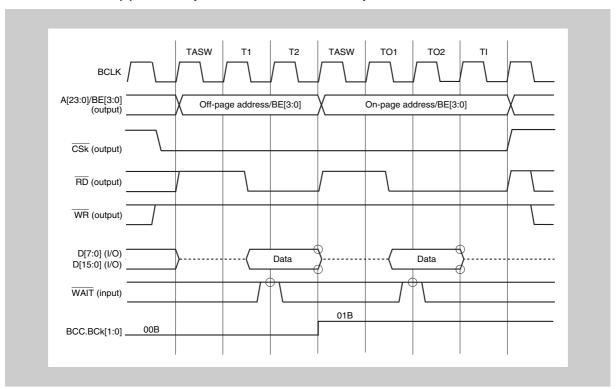

| 7.6                  | External Devices Interface Timing                                   | . 324 |

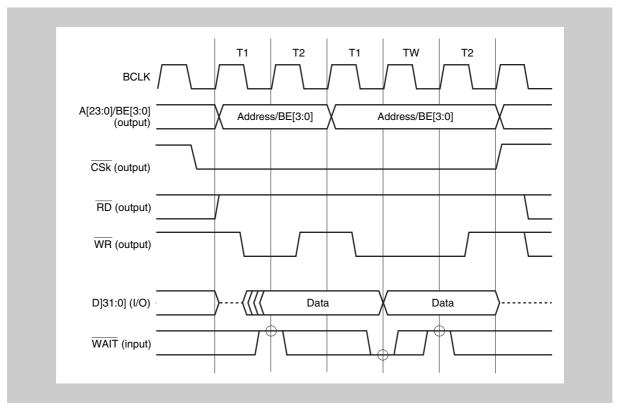

| 7.6.1                | Writing to external devices                                         | . 325 |

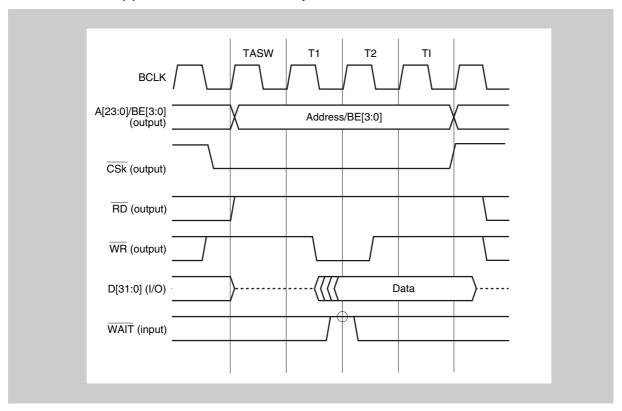

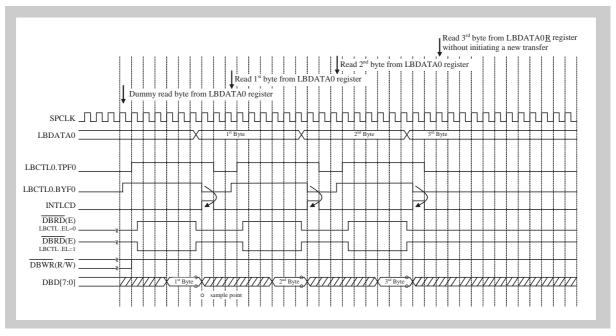

| ataSheet4U.com 7.6.2 | Reading from external devices                                       | 327   |

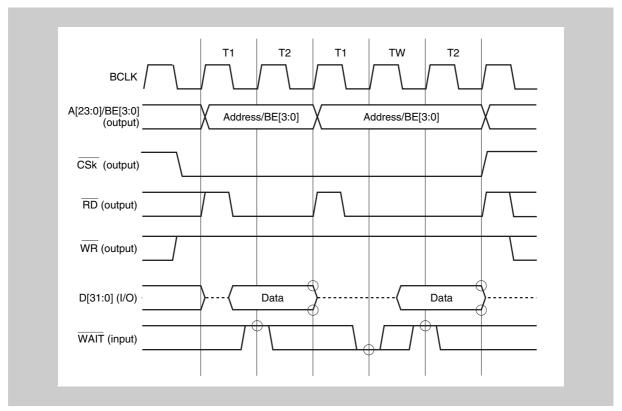

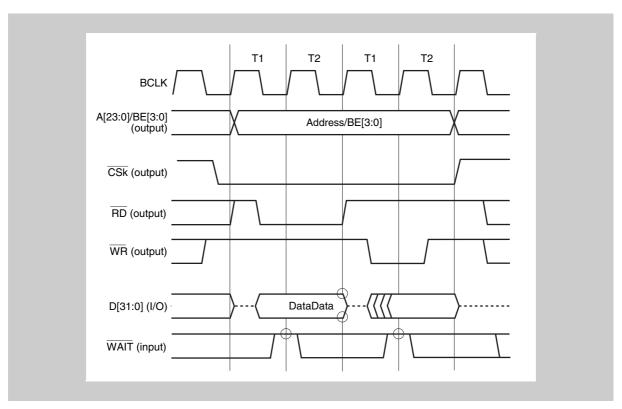

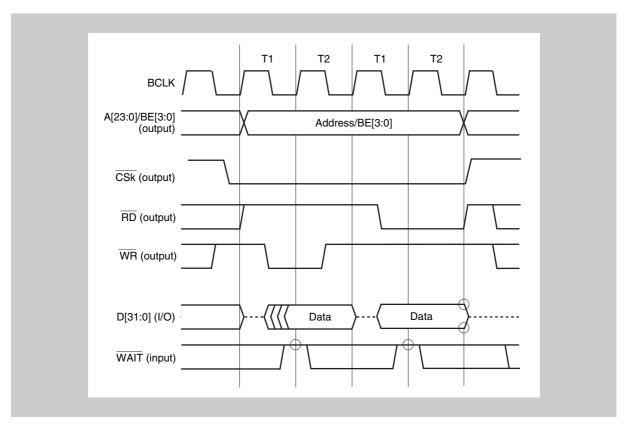

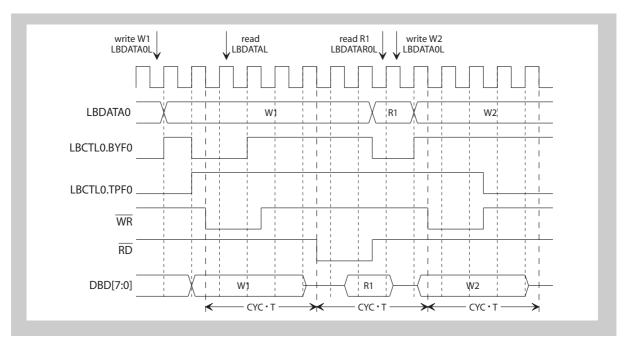

| 7.6.3                | Read-write operation on external devices                            |       |

| 7.6.4                | Write-read operation on external devices                            | 330   |

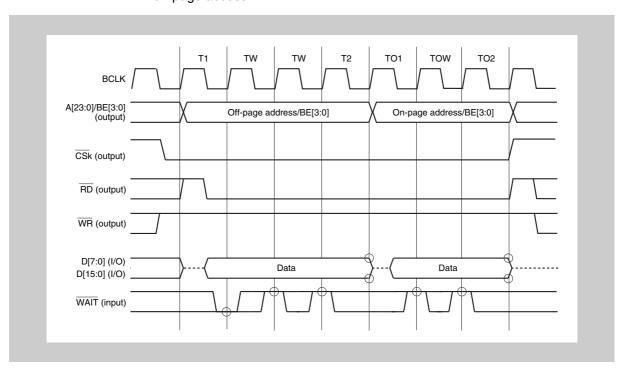

| 7.7                  | Page ROM Access Timing                                              | 331   |

| 7.7.1                | Half word/word access with 8-bit bus or word access with 16-bit bus | . 332 |

| 7.7.2                | Byte access with 8-bit bus or byte/half word access with 16-bit bus | 334   |

| 7.                    | B Data Access Order                                                 | . 336 |

|-----------------------|---------------------------------------------------------------------|-------|

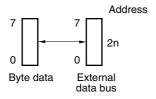

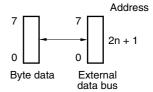

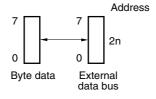

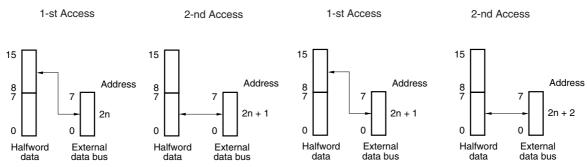

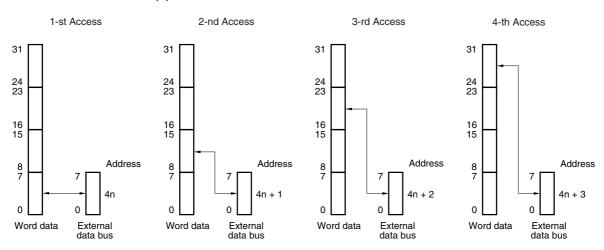

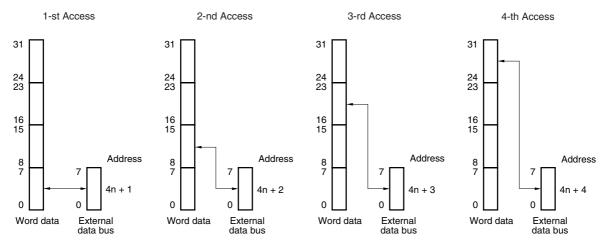

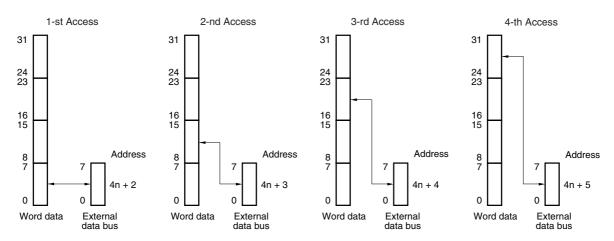

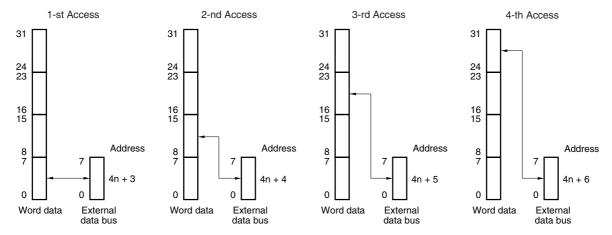

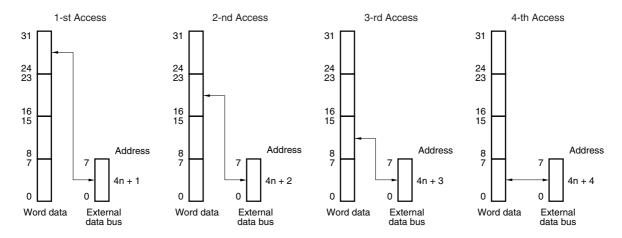

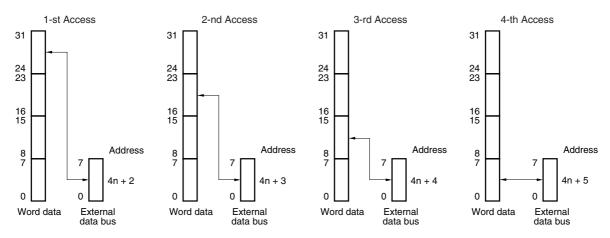

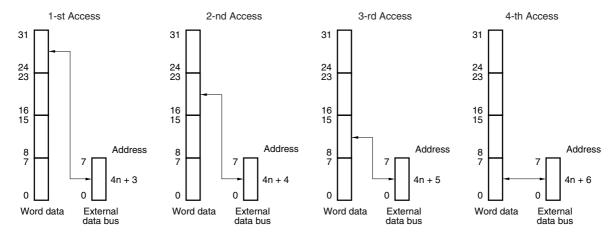

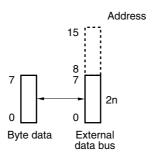

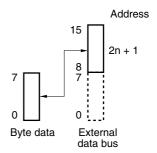

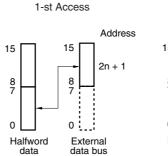

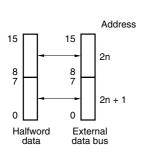

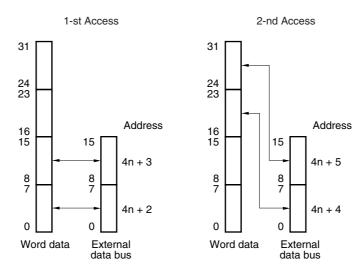

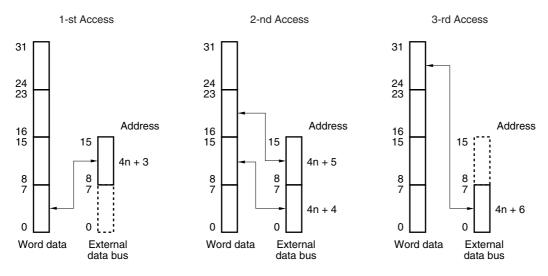

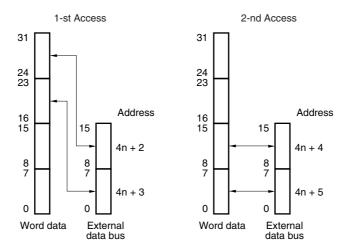

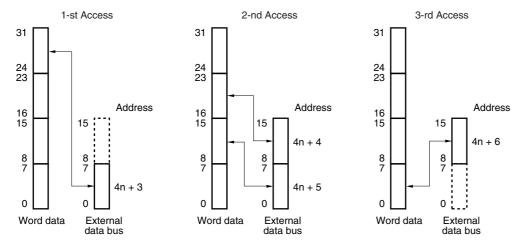

| 7.8.                  | 1 Access to 8-bit data busses                                       | . 336 |

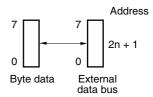

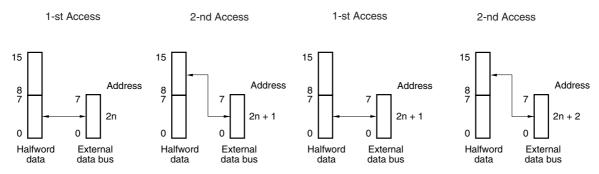

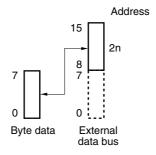

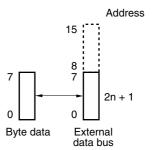

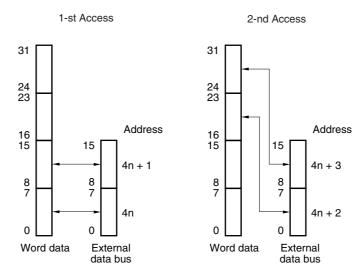

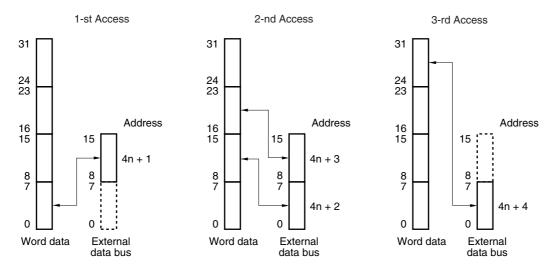

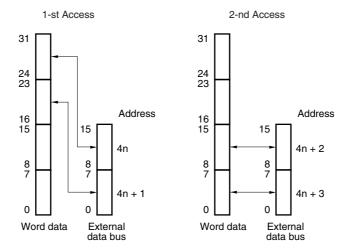

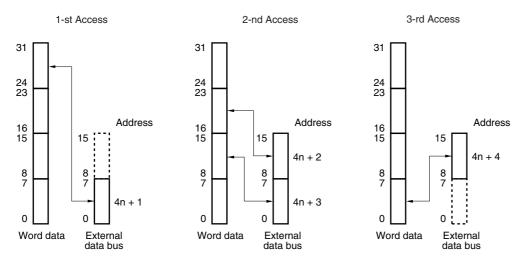

| 7.8.                  | 2 Access to 16-bit data busses                                      | . 342 |

| Chapter 8             | B DMA Controller (DMAC)                                             | . 349 |

| 8.                    | 1 Features                                                          | . 349 |

| 8.                    | Peripheral and CPU Clock Settings                                   | . 351 |

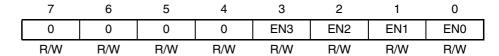

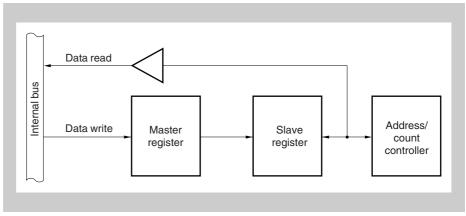

| 8.                    | B DMAC Registers                                                    | . 353 |

| 8.3.                  | 1 DMA Source address registers                                      | . 353 |

| 8.3.                  | 2 DMA destination address registers                                 | . 355 |

| 8.3.                  | BBCn - DMA transfer count registers                                 | . 357 |

| 8.3.                  | 3 3                                                                 |       |

| 8.3.                  | ÿ                                                                   |       |

| 8.3.                  | 3                                                                   |       |

| 8.3.                  |                                                                     |       |

| 8.                    | 4 DMA setup and retrigger                                           | . 365 |

| 8.4.                  |                                                                     |       |

| 8.4.                  | 2 DMA Retrigger                                                     | . 365 |

| 8.                    | 5 Automatic Restart Function                                        | . 366 |

| 8.                    | 6 Transfer Type                                                     | . 367 |

| 8.                    | 7 Transfer Object                                                   | . 367 |

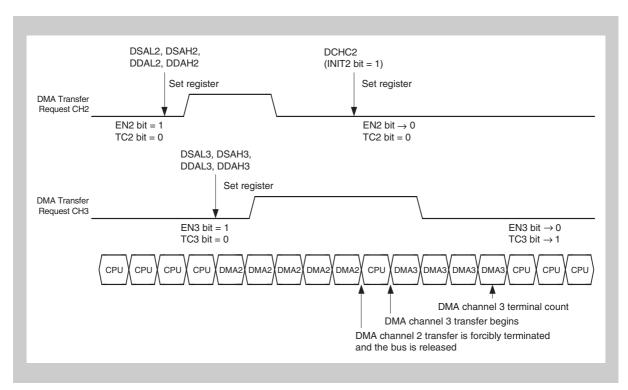

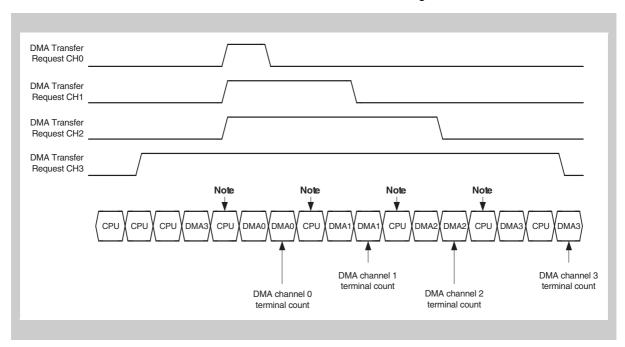

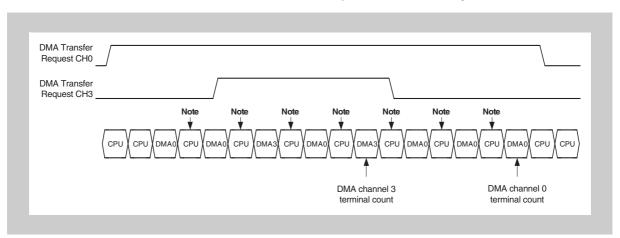

| 8.                    | B DMA Channel Priorities                                            | . 368 |

| 8.                    | DMA Transfer Start Factors                                          | . 368 |

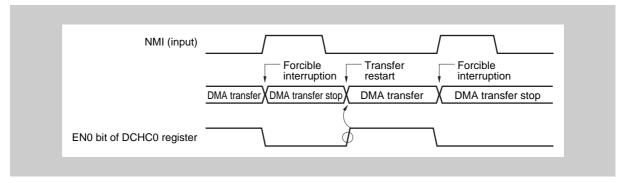

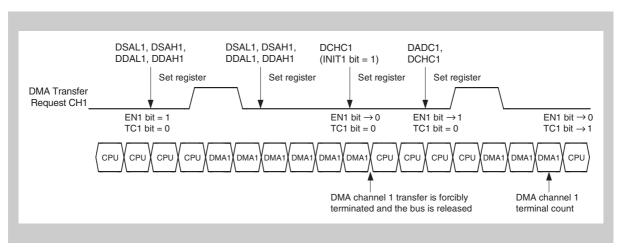

| 8.1                   | Forcible Interruption                                               | . 368 |

| 8.1                   | 1 Forcible Termination                                              | . 369 |

| 8.1                   | 2 DMA Transfer Completion                                           | . 371 |

| 8.1                   | 3 Transfer Mode                                                     | . 371 |

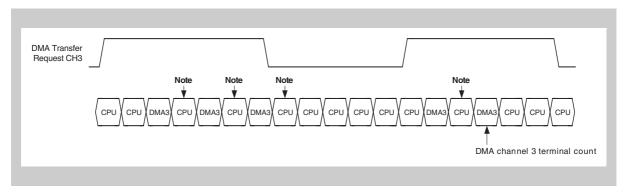

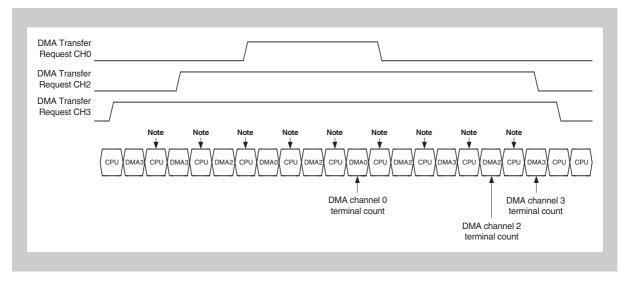

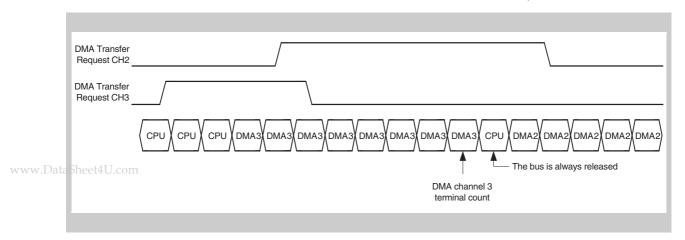

| 8.13.                 | 1 Single transfer mode                                              | . 371 |

| 8.13.                 | 2 Block transfer mode                                               | . 373 |

| 8.1                   | 4 Cautions                                                          | . 374 |

| 8.14.                 | 1 Simultaneous program execution and DMA transfer with internal RAM | . 374 |

| Chapter               | ROM Correction Function (ROMC)                                      | . 375 |

| 9.                    | 1 Overview                                                          | . 375 |

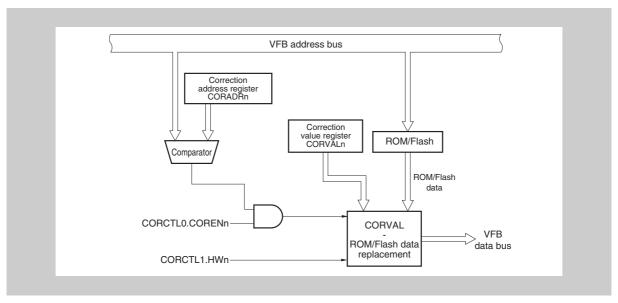

| 9.                    | 2 "Data Replacement" ROM Correction Unit                            | . 376 |

| .DataSheet4U.com 9.2. | Features                                                            | . 376 |

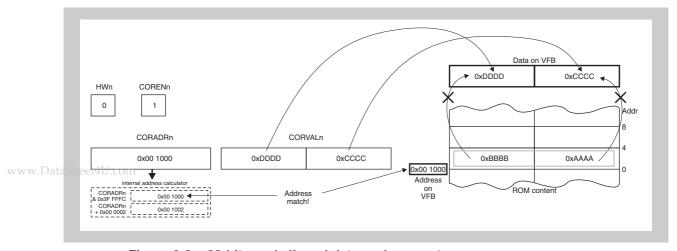

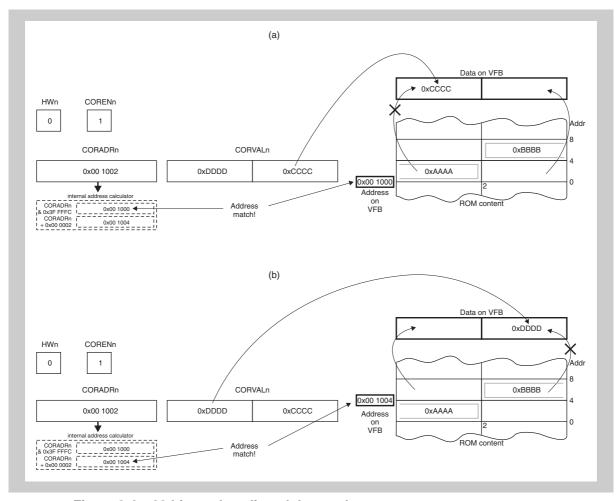

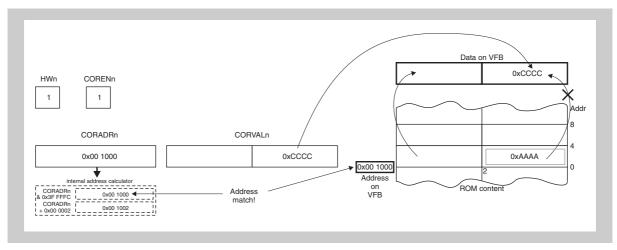

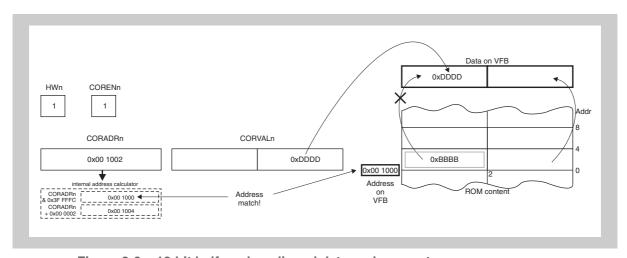

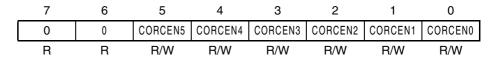

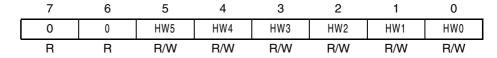

| 9.2.                  | 2 "Data Replacement" ROM correction operation                       | . 377 |

| 9.2.                  | 3 Setting of ROM correction addresses                               | . 380 |

| 9.2.                  | 4 "Data Replacement" ROM correction registers                       | . 382 |

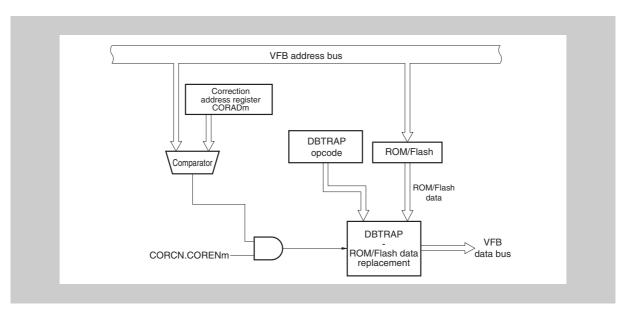

| 9.                    | 3 "DBTRAP" ROM Correction Unit                                      | . 387 |

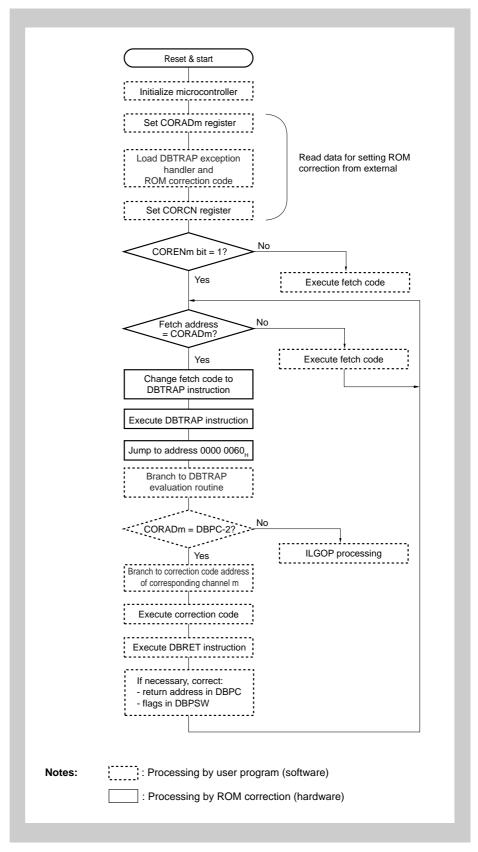

| 9.3.                  | 1 "DBTRAP" ROM correction operation                                 | . 388 |

|                       |                                                                     |       |

|                    | 9.3.2            | "DBTRAP" ROM correction registers                                    | . 390 |

|--------------------|------------------|----------------------------------------------------------------------|-------|

| Chapt              | er 10            | Code Protection and Security                                         | . 393 |

|                    | 10.1             | Overview                                                             | . 393 |

|                    | 10.2             | Boot ROM                                                             | . 393 |

|                    | 10.3             | N-Wire Debug Interface                                               | . 393 |

|                    | 10.4             | Flash Writer and Self-Programming Protection                         | . 395 |

|                    | 10.5             | Additional Firmware Functions                                        | . 396 |

|                    | 10.5.1           | ID-field                                                             |       |

|                    | 10.5.2           | Checksum calculation                                                 | . 396 |

|                    | 10.5.3           | Variable reset vector                                                | . 396 |

| Chapt              | er 11            | 16-bit Timer/Event Counter P (TMP)                                   | . 397 |